Štúdium režimov ROM a RAM multisim. Trvalá pamäť

Odoslanie dobrej práce do databázy znalostí je jednoduché. Použite nižšie uvedený formulár

Študenti, postgraduálni študenti, mladí vedci, ktorí pri štúdiu a práci využívajú vedomostnú základňu, vám budú veľmi vďační.

Uverejnené dňa http://www.allbest.ru/

Práca na kurze k téme

Vývoj mikroprocesorového systému so špecifikovanými parametrami RAM a ROM

Úvod

2. Rozšírenie adresných priestorov

Záver

Bibliografia

Úvod

Pozoruhodnou vlastnosťou mikroprocesorových systémov je ich vysoká flexibilita, schopnosť v prípade potreby rýchlo rekonfigurovať aj výrazné zmeny v riadiacich algoritmoch. Vykoná sa rekonfigurácia programovo bez výrazných výrobných nákladov. Vytvorenie mikroprocesorov umožňuje znížiť náklady a veľkosť technických prostriedkov spracovania informácií, zvýšiť ich výkon a znížiť spotrebu energie.

Charakteristické vlastnosti mikroprocesorových informačných a riadiacich systémov určených na automatizáciu technologických procesov:

*prítomnosť obmedzeného súboru jasne formulovaných úloh;

*požiadavky na optimalizáciu štruktúry systému pre konkrétnu aplikáciu;

*práca v reálnom čase, t.j. zabezpečenie minimálneho reakčného času na zmeny vonkajších podmienok;

*dostupnosť vyvinutého systému externých zariadení, ich široká škála;

*výrazný rozdiel vo funkčných úlohách;

*vysoké požiadavky na spoľahlivosť, berúc do úvahy dlhú dobu nepretržitej prevádzky;

*náročné prevádzkové podmienky;

*bezpečnosť automatický režim prevádzky alebo režimu za účasti operátora ako prvku systému.

Cieľom práce v tomto kurze je vyvinúť mikroprocesorový systém so špecifikovanými parametrami RAM a ROM, ako aj výpočet a návrh dodatočnej RAM a testovanie komponentov systému na elektrickú interakciu.

1. Rozdelenie adresného priestoru

Existuje mikroprocesorový systém s modulom procesora s nasledujúcimi charakteristikami:

· typ systémovej diaľnice – so samostatnými autobusmi;

· veľkosť adresného priestoru pamäťových zariadení (úložná kapacita) - 64 k;

· šírka pamäťovej dátovej zbernice - 16;

organizácia vstupno-výstupného systému:

· počet vstupných/výstupných portov - 2048;

· šírka dátovej zbernice vstupných/výstupných portov je 16;

riadiace signály zbernice:

· - nahrávanie do pamäťového zariadenia;

· - čítanie z pamäťového zariadenia;

· - nahrávanie v externé zariadenie;

· - čítanie z externého zariadenia;

K mikroprocesorovému systému pripojíme pamäťový modul obsahujúci: ROM, RAM1 a RAM2.

Počet slov ROM (ROM) vypočítame pomocou vzorca:

ROMx=2 MM=201=2

Počet slov RAM2 (RAM2ks) sa vypočíta takto:

1. vypočítajte možný počet slov Y pomocou vzorca:

Y = (ZUap – PZUks) / 3=(64*1024-2*16)/3=21 (k)

2. zaokrúhlite výsledný počet slov Y na RAM2ks pri splnení nasledujúcich podmienok:

a) RAM2ks? Y;

b) RAM2ks je násobok 2 n (n = 0, 1, 2, ...).

n = 4, 2 n = 16? 21.

Počet slov Y = 16

Počet slov RAM1 (RAM1ks) sa vypočíta podľa vzorca:

1. vypočítajte možný objem Y pomocou vzorca:

Y = (ZUap - RZUks - RAM2ks) / 3=(64*1024-2*16-16*16)/3=21 (k)

2. zaokrúhlite výsledný počet slov Y na RAM1ks, pri splnení nasledujúcich podmienok:

a) RAM1ks? Y;

b) RAM1ks je násobok 2 n (n = 0, 1, 2, ...)

n = 4, 2 n = 16? 21.

Čip ROM obsahuje: 1 adresovateľný vstup podľa počtu slov privedených na vstup, 8 dátových výstupov pre pripojenie RAM, vstupy pre riadiace signály - výber kryštálu a EO - stav výstupu.

Čipy RAM1 a RAM2 obsahujú: po 4 adresové vstupy, kombinované dátové vstupy/výstupy, vstupy pre riadiace signály CS - výber kryštálov, /R-zápis/čítanie.

Poďme navrhnúť prvok čipu ROM pomocou nástrojov aplikácie MS Visio 2010, ako je znázornené na obrázku 1.

Obrázok 1. Návrh čipu ROM

Vyberieme vhodný analóg pomocou. Najprv zobrazme v tabuľke priradenie kolíkov mikroobvodu, ako je uvedené v tabuľke. 1.

Tabuľka 1. Označenie pinov pamäťového čipu

|

názov |

Označenie |

|

|

Hodinový signál |

||

|

Stĺpce stroboskop adresy |

||

|

Stroboskop adresy riadkov |

||

|

Výber čipu |

||

|

Povolenie |

||

|

Čítanie |

||

|

Písať – čítať |

||

|

Povolenie na nahrávanie |

||

|

Výstupné rozlíšenie (čítanie) |

||

|

Údaje (informácie) |

||

|

Vstupné Data |

||

|

Výkon |

||

|

Adresa, údaje: vchod, výstup |

||

|

Údaje: vstup, výstup |

||

|

Regenerácia |

||

|

Programovanie |

||

|

Vymazanie |

||

|

Napájacie napätie |

||

|

Programovacie napätie |

||

|

Všeobecný kolík čipu |

Čipy ROM sa podľa spôsobu zadávania informácií do nich delia do troch skupín: maskovacie ROM, raz programované pomocou metódy šablóny (masky), raz programované metódou vypálenia prepojok na čip EEPROM a RPOM opakovane programované pomocou tzv. užívateľ.

Ak je pri navrhovaní mikroobvodov množstvo pamäte RAM malé (do 1024 bitov), pamäť sa zhromažďuje z jednotlivých klopných obvodov. Inak používajú knižnice hotových pamäťových modulov. Pri vývoji projektu pre FPGA majú hotové pamäťové moduly kapacitu 16, 32, 2048, 4096 bitov. IN najnovšie epizódy Kapacita modulu FPGA RAM sa zvýšila na 16K alebo 18K bitov. Šírku modulu RAM je možné nastaviť z nasledujúcich rozsahov: 1, 2, 4, 8 a 16 bitov. Zápis dát a adries do RAM modulu sa vykonáva vždy na hrane hodinového alebo zapisovacieho signálu, t.j. Vstup modulu možno považovať za vstup synchrónneho registra. Toto čítanie sa najčastejšie vykonáva v nasledujúcom hodinovom cykle po cykle príjmu adresy. Niekedy je na výstupe modulu RAM synchrónny register, ktorý si pamätá prečítané slovo. Zápis a čítanie z modulu je možné vykonávať pomocou princípu pipeline: v jednom taktovom cykle sa zapíše adresa nových údajov a načítané údaje sa vydajú na predchádzajúcu adresu. Na vytvorenie veľkoobjemovej pamäte RAM je systém zostavený z niekoľkých hotových modulov, dekodéra adries na výber modulu a výstupného multiplexora. Rôzne možnosti RAM v laboratóriu majú tri, dve alebo jednu zbernicu. V prvom prípade sú vstupné, výstupné dátové a adresové zbernice oddelené, v druhom prípade sú vstupné a výstupné dátové zbernice kombinované a v treťom prípade sa adresa aj dáta prenášajú multiplexne po jednej zbernici.

V súlade s úlohou vyberieme masku ROM, ktorej bloková schéma je znázornená na obrázku 2.

Obrázok 2. Bloková schéma masky ROM

Programovanie čipov PZUM sa vykonáva raz. Mikroobvod má tú vlastnosť, že je prchavý. Čipy ROM pracujú v režime čítania a ukladania. Na prečítanie informácií je potrebné zadať kód adresy a aktiváciu riadiacich signálov.

Zvolený typ mikroobvodu a zodpovedajúce charakteristiky sú znázornené na obrázku 3.

Obrázok 3. Pohľad na mikroobvod

Vyberte čip KP1610PE1. Charakteristiky mikroobvodu sú uvedené v tabuľke 2.

tabuľka 2

|

Typ čipu |

Kapacita, bit |

P výkon, mW |

Typ výstupu |

|||

Poďme navrhnúť prvok čipu RAM pomocou nástrojov aplikácie MS Visio 2010, ako je znázornené na obrázku 4.

elektrický pamäťový čip

Obrázok 4. Návrh čipu RAM

2. Rozšírenie adresného priestoru

K mikroprocesorovému systému navrhnutému v poslednej časti pripojíme prídavný modul pamäte s náhodným prístupom (RAM) obsahujúci N slov. Na určenie počtu pamäťových slov, ktoré potrebujete:

1. určiť veľkosť voľnej, najväčšej, adresnej oblasti

úložný priestor, Y;

Y=(ZUap - PZUks - RAM2ks - RAM1ks) / 3=(64*1024-2*16-16*16-16*16)/3=21 (k)

2. veľkosť Y zaokrúhlená na N slov spĺňajúca nasledujúce podmienky:

b) N je násobok 2 n (n=0,1,2,…).

RAM obsahuje: 7 adresových vstupov, kombinované dátové vstupy/výstupy, vstupy pre riadiace signály - výber kryštálu, - zápis, - čítanie.

3. Elektrická interakcia komponentov mikroprocesora

Skontrolujme elektrické rozhranie prvkov mikroprocesorového systému pomocou schémy zapojenia mikroprocesorového systému, realizovanej na základe reálnych prvkov.

Pri výpočtoch používame charakteristiky uvedené nižšie.

1. Modul CPU:

I0in, mA? - 2

I1in, mA? 0,05

Upit, V = 5 ± 5 %.

U1out, V? 2.7

U0out, V? 0,5

I0out, mA? 100

I1out mA? -5

Cout, pF? 10

Vstupné zariadenie, vstupné/výstupné zariadenie:

I0in, mA? -1.6

I1in, mA? 0,04

Upit, V = 5 ± 5 %.

U1out, V? 2.7

U0out, V? 0,5

I0out, mA? 48

I1out mA? -2.4

Cout, pF? 10

Zostávajúce mikroobvody sú v súlade s údajmi z pasu.

Záver

V súčasnosti sa podiel elektronických informačných zariadení a automatizačných zariadení neustále zvyšuje. Je to výsledok vývoja integrovanej technológie, ktorej zavedenie umožnilo zaviesť sériovú výrobu lacných, kvalitných mikroelektronických funkčných jednotiek, ktoré nevyžadujú špeciálnu konfiguráciu a nastavovanie. na rôzne účely, ktoré sú založené na elektronických prvkoch, ako sú polovodičové zariadenia. Vytvorenie polovodičových zariadení, ktoré sú rôznorodé a pozoruhodné svojimi vlastnosťami, určilo moderný pokrok v elektronike.

Na štúdium modernej elektroniky musíte v prvom rade poznať konštrukčné princípy a fyzikálne základy fungovania týchto zariadení, ich charakteristiky, parametre a najdôležitejšie vlastnosti, ktoré určujú možnosti ich použitia. Zároveň je veľmi dôležitá efektívnosť a presnosť získavania informácií, čo by malo byť uľahčené využitím rôznych technických prostriedkov.

V tejto kurzovej práci boli vyvinuté schémy elektrických obvodov a vybrané súčiastky mikroobvodov v súlade s danou možnosťou a skúmali sa možnosti ich výmeny a rozšírenia.

Bibliografia

1. Najlepší vyhľadávač elektronických komponentov

2. ***RUSKÁ ELEKTRONIKA***

3. Rádiový ventilátor

4. Telemaster

5. Promelektronika

6. MIKROELEKTRONICKÝ TRH (adresár)

7. ELEKTRONICKÉ KOMPONENTY Z CELÉHO SVETA

8. PRAKTICKÁ ELEKTRONIKA

9. Rádiový pilot - Schémy

10. Mitinský rozhlasový trh

11. Konferencia „Mikrokontroléry a ich aplikácie“

12. Micro-Chip LLC

13. Virtuálny obchod DESSY

14. ATMEL stránka v ruskom jazyku

15. Stránka schém

16. SPRIEVODCA RÁDIOVÝMI KOMPONENTMI

Uverejnené na Allbest.ru

Podobné dokumenty

Použitie digitálnych mikroobvodov na výpočet, správu a spracovanie informácií. Účel mikroprocesora a zariadenia mikroprocesorového systému, ich štruktúra a schémy zapojenia. Systémová zbernica procesora a distribúcia adresného priestoru.

kurzová práca, pridané 29.02.2012

Výpočet statického modulu Náhodný vstup do pamäťe a skladovanie. Stavebníctvo schematický diagram a časový diagram pamäťového modulu s nezávislým prístupom. Návrh aritmetickej logickej jednotky na delenie čísel s pevnou desatinnou čiarkou.

kurzová práca, pridané 13.06.2015

Hierarchia počítačových úložných zariadení. Mikroobvody a pamäťové systémy. Úložné zariadenia s náhodným prístupom. Princíp činnosti pamäťového zariadenia. Maximálne prípustné prevádzkové podmienky. Zvýšenie kapacity pamäte, bitovej hĺbky a počtu uložených slov.

kurzová práca, pridané 14.12.2012

Vývoj podnikovej štruktúry informačný systém. Dizajn adresného priestoru. Zdôvodnenie výberu hardvérovej konfigurácie klientske stanice a serverové vybavenie. Výpočet nákladov na vybavenie a softvér systémov.

kurzová práca, pridané 15.02.2016

Úvaha o blokovej schéme mikroprocesorového systému na spracovanie údajov. Popis architektúry mikrokontroléra ATmega161. Výpočet pamäte s náhodným prístupom. Štruktúra, účel adaptéra paralelného rozhrania, spôsoby jeho programovania.

kurzová práca, pridané 24.09.2010

Účel a návrh mikroprocesorového riadiaceho systému. Popis funkčný diagram mikroprocesorový riadiaci systém. Výpočet statických charakteristík meracieho kanála. Vývoj algoritmu pre fungovanie mikroprocesorového riadiaceho systému.

kurzová práca, pridané 30.08.2010

Vytvorenie blokovej schémy a všeobecného algoritmu pre prevádzku zariadenia. Odhad maximálnej chyby lineárneho snímača tlaku a normalizačného zosilňovača. Rozvoj prvkov základ elektrická schéma mikroprocesorový systém zberu dát.

kurzová práca, pridané 02.08.2015

Analýza možností konštrukčného riešenia a na základe toho výber optimálneho riešenia. Syntéza funkčného diagramu mikroprocesorového systému na základe analýzy zdrojových dát. Proces vývoja hardvéru a softvéru pre mikroprocesorový systém.

kurzová práca, pridané 20.05.2014

Štruktúra zariadenia na prenos informácií. Vývoj vysielacej a prijímacej časti podľa špecifikovaných parametrov. Vypracovanie funkčnej schémy zariadenia na prevod signálu a zariadenia na ochranu proti chybám, algoritmus jeho činnosti.

kurzová práca, pridané 3.12.2009

Štruktúra podnikového informačného systému organizácie. Vývoj adresného priestoru a systému DNS. Štruktúra domény CIS. Výber hardvérových a softvérových konfigurácií pre pracovné stanice a serverové zariadenia. Konfigurácia štandardných služieb.

Laboratórny robot č. 8

Predmet: Štúdia fungovania pamäte s náhodným prístupom (RAM))

1. Účel práce.

Preštudujte si fungovanie pamäťového zariadenia s náhodným prístupom v režimoch záznamu a čítania informácií, preskúmajte parametre časovania tohto zariadenia.

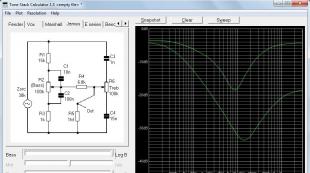

Použité vybavenie a nástroje:osobný počítač, prostredie Multisim 12.

Stručné teoretické informácie.

Štrukturálne sa každá RAM skladá z dvoch blokov -matice pamäťových prvkov a d e kódovač adresy. Z technologických dôvodov má matica najčastejšie dve súradnice A natívne dekódovanie adries - po riadkoch a stĺpcoch. Obrázok 1 zobrazuje maticu 16-bitového st tic RAM.

Matrica pozostáva zo 16 pamäťových buniek mem_i.

Schéma prvku matice (jedna bunka n A mäta) je znázornená na obr. Každá bunka n A pamäť je adresovaná vstupmi X, Y výberom ra dekodéry adresného riadku na str O kam Ax0...Ax3 a pozdĺž stĺpcov Ay0...Ay3. Výber sa uskutočňuje odoslaním s branové čiary signálnej matice log. "1". V tomto prípade sa spustí zvolená pamäťová bunka A je dvojvstupový prvok A (U 1 Obr. 2), príprava obvodov na čítanie a zápis na vstupe D 10… D 13 alebo výstupe DO0… DO 3 bitové zbernice.

Povoľovací signál na vydanie adresy je C.S. , ktorý sa privádza na vstup ra h riešenia počítadla adries ( Addr_cnt) alebo t a Aký je vstup dekodérov pripojených k výstupom elektromera.

Ryža. 1. 16-bitová matica RAM

Pri zápise bitu do pamäťovej bunky (obr. 2) sa na príslušnej bitovej zbernici nastaví 1 alebo 0, na vstupe WR/RD nastavte na „1“ po stránke O blokovanie počítadla alebo dekodéra adries signálom Spustia sa CS, prvky 2I U 1, U 2. Pozitívne pierko e signálna podložka z prvku U 2 prejde na vstup hodín Výsledkom je D-spúšť U 4 keď je v ňom napísaná 1 alebo 0, v A v závislosti od úrovne signálu D-vstup.

Ryža. 2. Schéma pamäťovej bunky mem_i.

Pri čítaní z pamäťovej bunky na vstupe WR/RD je nastavený na 0 a prvky sa spustia n vy U 1, U 3, U 5 a na vstup ENABLE OUTPUT vyrovnávacieho prvku U 6 príde povolenie Yu signál, výsledkom čoho je signál s Q-výstup D -spúšťač sa prenáša na bitovú zbernicu Urobte 0...Urobte 3.

Na kontrolu fungovania pamäťovej bunky sa používa generátor slov (obr. 3).

Ryža. 3. Predný panel generátora slov s nastaveniami obvodu

Na štúdium prevádzkových režimov RAM v laboratórnej práci sa používa mikroobvod HM-65642/883, čo je RAM statického typu. Oproti RAM znázornenej na obr.1 má kapacitu 8192 x 8-bitových buniek.

Údaje pre pripojenie mikroobvodu HM-65642/883 sú na obr. 4.

Ryža. 4. Označenie pinov čipu RAM typu NM-65642/883.

Riadenie sa vykonáva pomocou dvoch signálov: G - rozlíšenie vzorkovania, W - rozlíšenie záznamu a si informácie cie. Adresovateľné vstupy sú označené A , výstupné signály sú označené písmenom D.

Poradie práce.

Experiment 1. Štúdium bunky pamäte s náhodným prístupom (RAM).

Stiahnite si program Multisim 12 z Hlavného menu.

- Zostavte obvod znázornený na obr. 2.

- Nakreslite, aké by mali byť vstupné a výstupné signály na prvkoch I1 I6 pri zaznamenávaní, ukladaní a čítaní informácií.

- Nastavený na generátor slovkombinácia čísel, ktorá zabezpečuje zápis do pamäťovej bunky v súlade s číslom voľby binárnej jednotky.

- I6.

- Na generátore slov nastavte kombináciu čísel, ktorá zabezpečí uloženie binárnej jednotky v spomínanej pamäťovej bunke.

- Prezrite si osciloskopom a načrtnite signály na vstupoch a výstupoch prvkov I1 I6.

- Na slovnom generátore nastavte kombináciu čísel, ktorá zabezpečí čítanie binárnej jednotky z pamäťovej bunky.

- Prezrite si osciloskopom a načrtnite signály na vstupoch a výstupoch prvkov I1 I6.

Experiment 2. RAM Matrix Research.

- Zostavte obvod znázornený na obr. 5.

Obr.5. Schéma virtuálnej dosky s maticou RAM.

- Pomocou klávesov S 1… S 8 nastaviť adresy buniek pamäťovej oblasti (v súlade s číslom voľby) na čítanie obsahu týchto buniek. Výsledky zapíšte do tabuľky:

Údaje o adrese

K 0111

K+1 1011

K+2 1101

K+3 1110

- Zápis údajov pomocou kľúčov S 9…S 16 V články RAM podľa čísla variantu. Údaje sa zobrazujú v binárny kód pomocou LED a adresy buniek pomocou digitálnych indikátorov v hexadecimálnom kóde.

- Údaje, ktoré sa zapisujú do pamäťových buniek v súlade s číslom voľby, sú nasledovné:

a) beží „0“;

b) chod „1“;

c) beží „00“;

d) beží "11"

e) „zvyšujúca sa úroveň“;

f) „klesajúca úroveň“;

g) zmena zápisníka „11110000“;

h) „striedanie“ 1010101010.

5. Pri prepínaní tlačidiel adresy vykonajte dynamickú indikáciu S 1… S 8 na zodpovedajúce výstupy počítadla, ktoré prepína adresy buniek v dôsledku príjmu riadiacich impulzov z generátora.

6. Preskúmajte oscilogramy signálu v režime čítania údajov.

1. Názov a účel laboratórnej práce.

2. Názov každej položky práce, diagramy, výsledky meraní.

3. Závery na základe výsledkov výskumu.

Mikroprocesorové systémy používajú dva typy pamäťových zariadení (RAM): pamäť s náhodným prístupom (RAM) a pamäť iba na čítanie (ROM). V RAM je hlavným prevádzkovým režimom zápis a čítanie informácií. Informácie sa neustále aktualizujú, neukladajú sa dlho a po vypnutí zariadenia sa stratia. V ROM je hlavným prevádzkovým režimom iba čítanie informácií. K nahrávaniu dochádza pri výrobe mikroobvodu alebo pri jeho inštalácii do zariadenia.

Existujú rôzne typy ROM: programovateľná (PROM) a preprogramovateľná (RPM). Programovateľné pamäte ROM umožňujú používateľovi nezávisle zapisovať informácie do mikroobvodu pomocou špeciálnych zariadení. Takéto nahrávanie programov sa zvyčajne vykonáva po ich kontrole a odladení. Po zadaní do mikroobvodu nie je možné zmeniť informácie.

Preprogramovateľné ROM vám umožňujú opakovane vymazávať a znova zadávať informácie. V tomto prípade je možné použiť elektrické (EPRZU) alebo ultrafialové vymazanie (EPRZU - UV).

V závislosti od spôsobu organizácie pamäte sa rozlišuje medzi statickou a dynamickou pamäťou. Statické pamäte sa tvoria na základe spúšťacích buniek. Dynamické pamäte umožňujú, aby sa dáta počas ukladania menili alebo presúvali, napríklad pri ukladaní na kondenzátory, ktoré si vyžadujú periodické obnovovanie náboja. Dynamické pamäte neumožňujú čítanie kedykoľvek, ale majú veľmi vysokú hustotu záznamu informácií a nízku spotrebu energie.

Na výrobu pamäťových čipov sa používajú technológie TTL a MOS a ich odrody.

Na logických diagramoch RAM je označená RAM (dynamická RAM) - Random Acces Memory - pamäť s náhodným prístupom.

ROM sa označuje ako ROM (PROM - PROM, RPZU - RPROM) - Read Only Memory - pamäť len na čítanie.

Statická RAM. Produkované priemyslom veľké množstvo rôzne čipy RAM v rôznych sériách integrované obvody: K500, K1500, K537, K541, K565.

Ako príklad si vezmite čip K537RUZ, ktorý sa bežne používa ako statická RAM - obr. 6.6. Je vyrobený pomocou technológie CMOS, no z hľadiska úrovne signálu je kompatibilný s mikroobvodmi typu TTL. Kapacita pamäte je 4K, t.j. 4096 spúšťacích buniek. Čas odberu vzoriek nepresahuje 0,1 μs a čas zotavenia je 70 ns.

Vo vnútri mikroobvod obsahuje maticu pamäťových prvkov 64 x 64, dekodéry riadkových a stĺpcových adries, zosilňovače pre zápis a čítanie a riadiaci obvod. Označenia vstupov mikroobvodov:

12-bitová adresa pamäťovej bunky;

DO výstup - výstup dát;

DI vstup - vstup dát;

výber CS čipu;

Nastavujeme režim „zápis-čítanie“.

Symbol na pravom okraji symbol mikroobvod indikuje, že výstup má tretí vysokoimpedančný stav Z. Prevádzkový režim mikroobvodu v závislosti od stavu riadiacich signálov je znázornený v nasledujúcej tabuľke:

| C.S. | MY | Di | DO | Režim |

| Di | Z | Záznam | ||

| * | DO | Čítanie | ||

| * | * | Z | Skladovanie |

Symbol ◊ označuje ľubovoľný stav vstupu.

Kombináciou niekoľkých z týchto čipov môžete vytvoriť viacbitovú pamäť so 64 000 slovami.

Dynamická RAM obsiahnuté v mikroobvodoch série K565. Ich kapacita je až 64K. K regenerácii dochádza každé 2 ms. Mikroobvod má 4 prevádzkové režimy: zápis, čítanie, ukladanie, regenerácia. Regenerácia sa vykonáva prístupom ku každej pamäťovej bunke pomocou signálu RAS. Prirodzene, kým prebieha regenerácia, informácie sa nedajú zapisovať ani čítať.

Permanentná pamäť slúžia na ukladanie programov a iných trvalých informácií. Mikroobvody tohto typu uchovávajú informácie, keď je napájacie napätie vypnuté. Sú postavené na báze matice pamäťových prvkov TTL alebo MOS. Informácie sa do matrice zaznamenajú jednorazovo pomocou špeciálne vyrobenej fotomasky pokovovaním medzier medzi prvkami. Takáto fotomaska je oveľa drahšia ako samotný mikroobvod a vyrába sa pri objednávke veľkej dávky mikroobvodov. Čipy ROM sú súčasťou série integrovaných obvodov: K500,  K541, K568. K596, K1610. Na rns.6.10 je schéma ROM K568RES. Čip môže uložiť informácie o veľkosti 2-14 bajtov. Čítanie požadovaného bajtu sa vykonáva nastavením kódu adresy a signálu C.S. výber mikroobvodu.

K541, K568. K596, K1610. Na rns.6.10 je schéma ROM K568RES. Čip môže uložiť informácie o veľkosti 2-14 bajtov. Čítanie požadovaného bajtu sa vykonáva nastavením kódu adresy a signálu C.S. výber mikroobvodu.

Programovateľné ROM umožňujú nastaviť stav pamäťových buniek nie u výrobcu čipu, ale samotným vývojárom mikroprocesorového systému. Programovanie čipov EEPROM nastáva vypálením tavných spojov v obvodoch pamäťových buniek z externého zdroja pomocou špeciálneho zariadenia - programátora. Takéto ROM sú súčasťou nasledujúcej série mikroobvodov: K500, K556, K537, K541.

Elektrické programovateľné ROM Umožňuje viacnásobné programovanie pri zachovaní pamäte po vypnutí napájania. Pamäť je udržiavaná ukladaním náboja do štruktúry MOS. Doba uchovávania informácií za normálnych prevádzkových podmienok je roky.

Počet cyklov preprogramovania môže dosiahnuť 10 4 . V tomto prípade môžete vymazať alebo zmeniť všetky informácie alebo len selektívne. Mikroobvody ER ROM sú súčasťou radu integrovaných obvodov: K505, K558, K1601.

UV vymazateľné EPROM sú najbežnejšie. V nich je náboj odstránený z MOS štruktúry pamäťovej bunky ultrafialovým ožiarením kryštálu cez okienko v kryte mikroobvodu. Ožarovanie sa vykonáva špeciálnou ultrafialovou lampou počas 30 minút.

Príkladom RPZU-UF je mikroobvod K573RF. Počet cyklov preprogramovania tohto mikroobvodu je najmenej 25 a čas ukladania informácií bez napájania je najmenej 25 × 10 3 hodín.

Mikroobvody tohto typu vyžadujú ochranu pred náhodným vystavením svetelným tokom počas prevádzky.

LITERATÚRA

1. Zabrodin Yu.S. Priemyselná elektronika. - M.: Vyššia škola, 1982

2. Isakov Yu.L. atď. Základy priemyselnej elektroniky. inžinierska knižnica. - K.: Technika, 1976.

3. Gorbačov V.N., Chaplygin E.E. Priemyselná elektronika. - M.: Vyššia škola, 1988.

4. Kriyutafovič A.K., Trnfonyuk V.V. Základy priemyselnej elektroniky. - M.: Vyššia škola, 1985.

5. Rudenko V.S., Senko V.I., Trifonyuk V.R. Základy priemyselnej elektroniky. - K.: Vyššia škola, 1985.

6. Shilo V.L. Populárne digitálne mikroobvody. - M.: Rádio a komunikácia, 1988.

7. Krasnoproshna A.A., Skarzhepa V.A., Kravets P.I. Elektronika a mikroobvody. - K.: Vishcha School, 1989.

8. Aplikácia integrovaných obvodov. Upravil A. Williams. Preklad z angličtiny - M.: Mir. 19?".

9. Shcherbakov V.I., Grezdov G.I. Elektronické obvody založené na operačných zosilňovačoch. - K.: Technológia, 1983.

10. Granitov V.I. Fyzika polovodičov a polovodičových prvkov. - M.: Sovietsky rozhlas, 1977.

11. Samofalov K.G., Viktorov O.V., Kuznyak A.K. Mikroprocesory. Knižnica

inžinier.-K.: Technológia, 1986.

12.MirskiP G.Ya. Mikroprocesory v meracích prístrojoch. - M.: Rádio a spoje. 1984.

13. Vershinin O.E. Aplikácia mikroprocesorov pre automatizáciu technologických procesov. - L.: Energoatomnzdat, 1986.

|

3.1.Pamäťové čipy

Výhodou pamäte znázornenej na obr. 3.28 je, že takáto štruktúra je použiteľná pri navrhovaní veľkokapacitných pamätí. Nakreslili sme obvod 4x3 (pre 4 slová po 3 bitoch). Ak ho chcete rozšíriť na rozmery 4 x 8, musíte pridať 5 ďalších stĺpcov spúšťačov po 4 spúšťače, ako aj 5 vstupných a 5 výstupných riadkov. Ak chcete prejsť z veľkosti 4x3 na veľkosť 8x3, musíme pridať ďalšie štyri riadky spúšťačov po troch spúšťačoch, ako aj riadok adresy A2. Pri tejto štruktúre musí byť počet slov v pamäti mocninou dvoch pre maximálnu účinnosť a počet bitov na slovo môže byť ľubovoľné číslo. Pretože technológia integrovaných obvodov je vhodná pre

vyrábajúce čipy s vnútornou štruktúrou opakovateľného rovného povrchu, pamäťové čipy sú na to ideálnou aplikáciou. Ako technológia napreduje, počet bitov, ktoré môžu byť obsiahnuté na jednom čipe, sa neustále zvyšuje, zvyčajne sa zdvojnásobuje každých 18 mesiacov (Mooreov zákon). S príchodom veľkých čipov nie sú malé čipy vždy zastarané kvôli kompromisom medzi výhodami kapacity, rýchlosti, výkonu, ceny a rozhrania. Typicky sú najväčšie moderné čipy veľmi žiadané, a preto stoja oveľa viac za bit ako menšie čipy.

Pre akékoľvek množstvo pamäte existuje niekoľko rôznymi spôsobmi orgán-

nizácia mikroobvodu. Na obr. Obrázok 3.30 zobrazuje dve možné štruktúry 4 Mbit čipu: 512 Kx8 a 4096 Kxl. (Veľkosti pamäťových čipov sa zvyčajne udávajú v bitoch a nie v bajtoch, preto sa tu budeme držať tejto konvencie.) Na obr. 3.30 a môžete vidieť 19 riadkov adresy na prístup k jednému z 219 bajtov a 8 dátových riadkov na načítanie alebo uloženie zvoleného bajtu.

Urobme malú poznámku o terminológii. Na rovnakých záveroch

vysoké napätie spôsobuje nejakú akciu, na iných - nízke napätie. Aby sme sa vyhli nejasnostiam, použijeme výraz „nastaviť signál“, keď dôjde k akcii, namiesto toho, aby sme povedali, že sa napätie zvýši alebo zníži. Pre niektoré piny teda nastavenie signálu znamená nastavenie na 1 a pre iné nastavenie na 0. Názvy pinov, ktoré sú nastavené na 0, obsahujú lištu v hornej časti. Signál CS je nastavený na 1 a signál CS je nastavený na 0. Opačný pojem je "reset".

Teraz sa vráťme k nášmu mikroobvodu. Keďže počítač zvyčajne obsahuje veľa pamäťových čipov, na výber požadovaného čipu je potrebný signál, aby čip, ktorý potrebujeme, reagoval na volanie, ale zvyšok nie.

Práve na tento účel sa používa signál CS (Chip Select). Inštaluje sa na spustenie čipu. Okrem toho potrebujeme spôsob, ako odlíšiť čítanie od zápisu. Signál WE (Write Enable) sa používa na označenie, že dáta by sa mali skôr zapisovať ako čítať. Nakoniec je signál (Output Enable) nastavený na produkciu výstupných signálov. Ak tento signál nie je prítomný, je výstup odpojený od zvyšku obvodu. Na obr. 3.30 je použitá iná schéma adresovania matica 2048x2048 jednobitových buniek, čo je 4 Mbit, aby ste získali prístup k mikroobvodu, aby ste to urobili, číslo I-bitu tohto riadku sa privedie na kolíky adresy sa nastaví (Row Address Strobe - potom sa číslo odošle do stĺpca adresy a nastaví sa CAS signál (Column Address Strobe - stĺpcový impulz adresy).

Veľké pamäťové čipy sa často vyrábajú ako matice mxn, ku ktorým sa pristupuje podľa riadkov a stĺpcov. Táto organizácia pamäte znižuje počet potrebných pinov, ale na druhej strane spomaľuje prístup k čipu, pretože sú potrebné dva cykly adresovania: jeden pre riadok a druhý pre stĺpec. Na urýchlenie tohto procesu môžu niektoré čipy volať adresu riadka a potom viacero adries stĺpcov, aby získali prístup k po sebe nasledujúcim bitom riadku.

Pred mnohými rokmi boli zvyčajne usporiadané najväčšie pamäťové čipy

ako je znázornené na obr. 3,30, b. Ako slová rástli z 8 na 32 bitov a vyššie, používanie takýchto čipov sa stávalo nepohodlným. Na zostavenie 32-bitovej slovnej pamäte zo 4096 Kxl čipov je potrebných 32 čipov bežiacich paralelne. Týchto 32 čipov má celkovú kapacitu minimálne 16 MB. Ak použijete čipy 512 Kx8, budete potrebovať iba 4 čipy, no kapacita pamäte bude 2 MB. Aby sa vyhli 32 čipom, väčšina výrobcov vyrába rodiny čipov s dĺžkami slov 1, 4, 8 a 16 bitov.

3.2.RAM a ROM

Všetky typy pamätí, o ktorých sme doteraz uvažovali, majú jednu spoločnú vlastnosť: dokážu informácie zapisovať aj čítať. Táto pamäť sa nazýva RAM (random access memory). Existujú dva typy pamäte RAM: statická a dynamická. Statická RAM je navrhnutá pomocou D klopných obvodov. Informácie v pamäti RAM sa uchovávajú dovtedy, kým je do nej privádzaná energia: sekundy, minúty, hodiny a dokonca aj dni. Statická RAM je veľmi rýchla. Typicky je prístupový čas niekoľko nanosekúnd. Z tohto dôvodu sa statická RAM často používa ako vyrovnávacia pamäť L2.

Naproti tomu dynamická RAM nepoužíva spúšťače. Dynamický

RAM je pole buniek, z ktorých každá obsahuje tranzistor a malý kondenzátor. Kondenzátory je možné nabíjať a vybíjať, čo im umožňuje ukladať nuly a jednotky. Pretože elektrický náboj má tendenciu miznúť, každý bit v DRAM sa musí obnovovať (dobíjať) každých pár milisekúnd, aby sa zabránilo úniku dát. Keďže sa o aktualizáciu musí starať externá logika, dynamická RAM vyžaduje zložitejšie rozhranie ako statická RAM, aj keď túto nevýhodu kompenzuje jej väčšia kapacita.

Keďže DRAM potrebuje iba 1 tranzistor a 1 kondenzátor na bit (statická RAM potrebuje prinajlepšom 6 tranzistorov na bit), DRAM má veľmi vysokú hustotu zápisu (veľa bitov na čip). Z tohto dôvodu je hlavná pamäť takmer vždy postavená na báze dynamickej RAM. Dynamické RAM sú však veľmi pomalé (čas prístupu trvá desiatky nanosekúnd). Kombinácia vyrovnávacej pamäte založenej na SRAM a hlavnej pamäte založenej na DRAM teda spája výhody oboch zariadení.

Existuje niekoľko typov dynamickej pamäte RAM. Najstarší typ, ktorý

Prvý, ktorý sa stále používa, je FPM (Fast Page Mode). Táto RAM je matica bitov. Hardvér predstavuje adresu riadka a potom adresy stĺpca (tento proces sme opísali, keď sme hovorili o pamäťovom zariadení znázornenom na obrázku 3.30, 6).

FPM sa postupne nahrádza EDO1 (Extended Data Output - pamäť s rozšír

známe výstupné schopnosti), čo vám umožňuje získať prístup k pamäti pred dokončením predchádzajúceho prístupu. Tento zreťazený režim nezrýchľuje prístup k pamäti, ale zvyšuje sa priepustnosť, vydávanie viac slov za sekundu. FPM aj EDO sú asynchrónne. Naproti tomu takzvaná synchrónna dynamická RAM je riadená jediným hodinovým signálom. Toto zariadenie je hybridom statickej a dynamickej pamäte RAM. Synchrónna dynamická RAM sa často používa pri výrobe veľkej vyrovnávacej pamäte. Možno, túto technológiu v budúcnosti bude najviac

výhodnejšie pri výrobe hlavnej pamäte.

RAM nie je jediným typom pamäťového čipu. V mnohých prípadoch údaje

musia byť uložené aj po vypnutí napájania (napr hovoríme o o hračkách, rôznych zariadeniach a strojoch). Navyše po inštalácii by sa nemali meniť ani programy, ani údaje. Tieto požiadavky viedli k vzniku ROM (pamätí len na čítanie), ktoré neumožňujú zmenu alebo vymazanie informácií v nich uložených (či už úmyselne alebo náhodne). Dáta sa zapisujú do ROM počas výroby. Na tento účel sa vytvorí šablóna so špecifickou sadou bitov, ktorá sa aplikuje na fotocitlivý materiál a potom sa vyleptajú otvorené (alebo uzavreté) časti povrchu.

Jediný spôsob, ako zmeniť program v ROM, je zmeniť celý čip. ROM sú oveľa lacnejšie ako RAM, ak si ich objednáte vo veľkých množstvách, aby ste pokryli náklady na výrobu šablóny. Po opustení výroby však zmeny neumožňujú a medzi odoslaním objednávky na ROM a jej dokončením môže uplynúť niekoľko týždňov. Aby spoločnostiam uľahčili vývoj nových zariadení založených na ROM, boli uvoľnené programovateľné ROM. Na rozdiel od bežných ROM sa dajú naprogramovať priamo v teréne, čím sa skrátia dodacie lehoty. Mnoho programovateľných ROM obsahuje rad malých taviteľných prepojení. Ak vyberiete, môžete vypáliť konkrétny prepojok požadovaný riadok a požadovaný stĺpec a potom aplikujte vysoké napätie na konkrétny kolík čipu.

Ďalším vývojom tohto radu je vymazateľná programovateľná ROM, ktorú je možné nielen naprogramovať v prevádzkových podmienkach, ale aj z nej vymazať informácie. Ak je kremenné okno v tejto ROM vystavené silnému ultrafialovému svetlu na 15 minút, všetky bity sa nastavia na 1.

Ak je počas jednej fázy návrhu potrebné vykonať veľa zmien, vymazateľné ROM sú oveľa efektívnejšie z hľadiska nákladov ako bežné programovateľné ROM, pretože sa dajú používať znova a znova. EPROM sú zvyčajne navrhnuté rovnakým spôsobom ako statická RAM. Napríklad mikroobvod 27C040 má štruktúru, ktorá je znázornená na obr. 3.30, a, a takáto štruktúra je typická pre statickú RAM.

Ďalším stupňom je elektronicky preprogramovateľná ROM, z ktorej môžete

ale vymazať informácie tým, že na ne použijete impulzy, a ktorý nie je potrebné umiestniť do špeciálnej komory, aby bol vystavený ultrafialovým lúčom. Okrem toho preprogramovať toto zariadenie, na programovanie ho netreba vkladať do špeciálneho stroja, na rozdiel od vymazateľnej programovateľnej ROM, ale na druhej strane sú najväčšie elektronické preprogramovateľné ROM 64-krát menšie ako bežné vymazateľné ROM a fungujú o polovicu pomalšie. EEPROM nemôžu konkurovať DRAM a statickej RAM, pretože sú 10-krát pomalšie, majú 100-krát menšiu kapacitu a sú oveľa drahšie. Oni

sa používajú iba v situáciách, keď je potrebné zachovať informácie pri vypnutí napájania.

Modernejším typom elektronicky programovateľných ROM je flash pamäť. Na rozdiel od EPROM, ktorá sa vymazáva vystavením ultrafialovému svetlu, a EPROM, ktorá sa vymazáva bajt po byte, sa flash pamäť vymazáva a zapisuje v blokoch. Ako každú elektronicky programovateľnú ROM, aj flash pamäť je možné vymazať bez jej odstránenia z čipu. Mnoho výrobcov vyrába malé dosky plošných spojov, obsahujúci desiatky megabajtov flash pamäte. Používajú sa na ukladanie obrázkov v digitálnych fotoaparátoch a na iné účely. Možno raz flash pamäť nahradí disky, čo by bol obrovský krok vpred vzhľadom na prístupové časy 100 sekúnd. Základné technický problém V tento moment je, že pamäť flash sa opotrebuje po 10 000 vymazaniach a disky môžu vydržať roky bez ohľadu na to, koľkokrát boli prepísané. Stručný opis

rôzne druhy pamäť je uvedená v tabuľke. 3.2.

Prednáška 8. Riadiace a interfejsové mikroobvody.

1. Procesorové čipy.

2. Pneumatiky a princípy ich činnosti.

3. Prostriedky rozhrania.

MINISTERSTVO školstva a vedy Ruskej federácie

FEDERÁLNA ŠTÁTNA ROZPOČTOVÁ vzdelávacia inštitúcia

vyššie odborné vzdelanie

Ťumeňská štátna univerzita pre ropu a plyn

Ústav kybernetiky, informatiky a komunikácií

KURZOVÁ PRÁCA

Stavebníctvo vnútorná pamäť procesorový systém

v odbore: "Informatika"

Technická úloha

Možnosť - 6

Zostavte vnútornú pamäť procesorového systému pozostávajúcu z ROM a statickej RAM.

Bitová veľkosť ША – 20 , ШД – 8 .

Adresy pokryté ROM - 00000-03FFF

Adresy pokryté RAM – 80000-9FFFF

Kapacita čipu ROM - 16K*8

Kapacita čipu RAM - 64K*4

Úvod ……………………………………………………………………………… 4

1 Teoretická časť

1.1 Všeobecná štruktúra IPU…………………………………………………………………5

1.2 Pamäťový subsystém MPS………………………………………………………7

1.3 Pamäťové zariadenia…………………………………………………………...9

1.4 Statická RAM. Konštrukčné princípy………………………………………...11

1.5 Princíp zaznamenávania/čítania informácií………………………………………...13

1.6 Konštrukcia pamäťového priestoru danej veľkosti………………..14

2 Praktická časť

2.1 Určenie kapacity pamäte ROM a RAM ................................................ ........................16

2.2 Štruktúra pamäte ROM a RAM……………………………………………………………………………….. 19

2.3 Všeobecná štruktúra pamäte………………………………………………...20

Záver……………………………………………………………………………… 21

Referencie……………………………………………………………… 22

Úvod

Informácie cirkulujúce vo výpočtovom systéme sú uložené v pamäti. Hlavnými kritériami pre hodnotenie úložného zariadenia sú kapacita, rýchlosť a spotreba energie.

Pamäť počítača poskytuje podporu pre jednu z najdôležitejšie funkcie Moderný počítač má schopnosť uchovávať informácie na dlhú dobu.

V závislosti od umiestnenia v počítačovom systéme sa pamäť delí na vnútornú (RAM, SRAM a ROM) a externú (rôzne úložné zariadenia).

V teoretickej časti tejto práce sa zaoberáme počítačovou pamäťou, jej typmi a klasifikáciami, v praktickej časti je realizovaná konštrukcia vnútornej pamäte procesorového systému.

Na konci práce sa urobí záver a uvedie sa zoznam odkazov.

1.1 Všeobecná štruktúra IPJ

Mikroprocesor (MP) - centrálna časť každého mikroprocesorového systému (MPS) - obsahuje aritmeticko-logickú jednotku (ALU) a centrálnu riadiacu jednotku (CCU), ktorá realizuje príkazový cyklus. MP môže fungovať len ako súčasť MPS, ktorá obsahuje okrem MP aj pamäť, vstupno/výstupné zariadenia, pomocné obvody (generátor hodín, ovládače prerušenia a priamy prístup do pamäte (DMA), ovládačov zbernice, blokovacích registrov atď.

V každom MPS možno rozlíšiť tieto hlavné časti (subsystémy):

externé zariadenia (externé úložisko + vstupné/výstupné zariadenia);

podsystém prerušenia;

podsystém priameho prístupu do pamäte.

modul procesora;

Obrázok 1 – Štruktúra MPS s rozhraním „Common Bus“.

Komunikácia medzi procesorom a ostatnými MPS zariadeniami môže prebiehať pomocou princípov radiálnych spojení, spoločnej zbernice alebo kombinovanej metódy. V jednoprocesorových MPS, najmä 8- a 16-bitových, sa najviac rozšíril komunikačný princíp „Common Bus“, pri ktorom sú všetky zariadenia pripojené k rozhraniu rovnakým spôsobom (obrázok 1).

Všetky signály rozhrania sú rozdelené do troch hlavných skupín – dátové, adresové a riadiace. Početné typy rozhraní „Common Bus“ zabezpečujú prenos po samostatných alebo multiplexných linkách (zbernice). Napríklad rozhranie Microbus, na ktorom pracuje väčšina 8-bitových MPU na báze i8080, prenáša adresy a dáta na samostatných zberniciach, ale niektoré riadiace signály sa prenášajú na dátovej zbernici. Rozhranie Q-bus používané v mikropočítačoch od DEC (domáci analóg - mikroprocesory série K1801) má multiplexnú adresovú/dátovú zbernicu, cez ktorú sa tieto informácie prenášajú s časovým delením. Prirodzene, ak existuje multiplexná zbernica, je potrebné do riadiacich liniek zaradiť špeciálny signál, ktorý identifikuje typ informácie na zbernici.

Informácie sa vymieňajú cez rozhranie medzi dvoma zariadeniami, z ktorých jedno je aktívne a druhé pasívne. Aktívne zariadenie generuje adresy pasívnych zariadení a riadiace signály. Aktívnym zariadením je zvyčajne procesor a pasívnym zariadením je vždy pamäť a niektoré počítače. Avšak niekedy môžu vysokorýchlostné hostiteľské zariadenia fungovať ako hlavné (aktívne zariadenie) na rozhraní, ktoré riadi výmenu s pamäťou.

Koncepcia „Common Bus“ predpokladá, že prístup ku všetkým zariadeniam MPS sa uskutočňuje v jedinom adresnom priestore, avšak s cieľom rozšíriť počet adresovateľných objektov v niektorých systémoch adresné priestory pamäte a pamäte a niekedy dokonca aj programová pamäť a dátová pamäť, sú umelo oddelené.

12 MPS pamäťový subsystém

Distribúcia adresného priestoru.

Objem adresného priestoru MPS s rozhraním „Common Bus“ je určený najmä bitovou šírkou adresovej zbernice a okrem toho rozsahom riadiacich signálov rozhrania. Riadiace signály môžu určiť typ objektu, ku ktorému sa pristupuje (RAM, pamäť, zásobník, špecializovaná ROM atď.). Ak MP nevytvára signály identifikujúce pasívne zariadenie (alebo sa nepoužívajú v MPS), na výber sa použijú iba adresné riadky. Počet adresovateľných objektov je v tomto prípade 2 k, kde k je šírka adresovej zbernice. Takýto adresný priestor budeme nazývať „single“. Niekedy hovoria, že pamäťové zariadenia v jednom adresnom priestore sú „mapované v pamäti“, t.j. Adresy JV zaberajú adresy pamäťových buniek. Príklad organizácie výberu zariadení v jedinom adresnom priestore MPS na báze i8080 a distribúcia adresného priestoru sú zobrazené na obrázku 2 a obrázku 3, v tomto poradí.

Obrázok 2 – Štruktúra jedného adresného priestoru

Obrázok 3 – Príklad rozloženia jedného adresného priestoru

Pri malom množstve pamäte v MPS je vhodné použiť niektoré riadky adries priamo ako selektorové riadky (obrázok 4), čo vám umožní znížiť množstvo MPS zariadení odstránením selektora adries. Adresný priestor sa však využíva extrémne neefektívne.

Pri použití informácií o type zariadenia, ku ktorému sa pristupuje, môžu byť rovnaké adresy priradené rôznym zariadeniam, pričom výber sa vykonáva pomocou riadiacich signálov.

Väčšina poslancov teda poskytuje informácie o type odvolania v tej či onej forme. Výsledkom je, že väčšina rozhraní obsahuje samostatné riadiace linky pre prístup k pamäti a vstup / výstup a menej často - zásobník alebo špecializovanú ROM. V dôsledku toho môže celkový objem adresného priestoru MPS prekročiť 2 k.

Obrázok 4 – Použitie riadkov adresy na priamy výber zariadenia

1.3 Pamäťové zariadenia

Pamäťové zariadenia mikroprocesorového systému (MPS) môžu byť externé (pevný disk, disková jednotka, CD-ROM atď.) a interné (RAM, ROM).

Táto práca v kurze skúma vnútornú pamäť MPS, ktorá môže byť:

len na čítanie (ROM) alebo ROM,

pamäť s náhodným prístupom (RAM) alebo pamäť s náhodným prístupom.

Na druhej strane sa ROM líšia v spôsobe, akým zaznamenávajú/prepisujú informácie nasledovne.

ROM sú pamäťové zariadenia len na čítanie založené na diódových matriciach. Matrice sa vypaľujú vo výrobnom závode, používateľ nemôže nič meniť (obrázok 5). Pri odovzdávaní U> U prídavná dióda vyhorí a zostane prepojka; s vypálenou diódou U uzol = 0; s funkčnou diódou U uzol = 1

PROM sú preprogramovateľné ROM (matice sú užívateľovi dodávané s úrovňou 1 vo všetkých uzloch, užívateľ môže maticu napáliť iba raz podľa svojho programu).

RPOM – preprogramovateľná (t.j. opakovane programovateľná) ROM.

Obrázok 5 – Prvok diódovej matice.

Podľa spôsobu vymazania informácií môžu byť ROM: ultrafialové a elektrické.

Pamäť s náhodným prístupom (RAM) môže byť dynamická (DRAM) alebo statická (SRAM).

V dynamickej RAM, postavenej na MOS-tranzistorových článkoch s dodatočnou kapacitou, informácie po prečítaní miznú, takže je potrebná ich regenerácia (obnovenie), čo znamená, že takáto RAM má napriek zjavnej lacnosti nízky výkon.

Statická RAM, postavená na spúšťacích bunkách, ukladá informácie po prečítaní a nevyžaduje regeneráciu, má vysoký výkon, aj keď je podstatne drahšia ako dynamická RAM.

Moderné konštrukcie RAM kombinujú obe technológie (SDRAM).

1.4 Statická RAM. Konštrukčné princípy

Obrázok 6 – Statický pamäťový čip

Adresová zbernica (obrázok 6) je pripojená k pamäťovému čipu cez N adresovateľné vstupy: A 0 – A N –1 .

Dátová zbernica je pripojená cez vstupy/výstupy D, ktorých počet závisí od toho, koľko matíc sa nachádza v kryštáli.

CS – kryštálový vzorkový vstup, riadi pripojenie dátovej vyrovnávacej pamäte na zbernicu.

– vstup pre zápis/čítanie, určuje pripojenie vstupnej alebo výstupnej vyrovnávacej pamäte dát k dátovej zbernici.

Uvažujme o princípe výberu pamäťovej bunky podľa adresy.

Vstupy adresovej zbernice sú pripojené k riadkovému a stĺpcovému dekodéru (DC) matice. Predpokladajme, že k mikroobvodu sú pripojené štyri adresné linky (A 0 - A 3) a linky A 0, A 1 sú napájané do riadku DC a linky A 2, A 3 sú napájané do stĺpca DC.

Obrázok 7 – Výber bunky podľa adresy: a – spúšťač; b – maticový prvok

Predpokladajme, že na adresových vstupoch je uvedená adresa 9, t.j. 1001.

Teda riadok DC pri A 0 = 1, A 1 = 0 nastaví 1 na výstupe 1 a stĺpec DC pri A 2 = 0, A 3 = 1 nastaví 1 na výstupe 2.

Spúšťače sú umiestnené vo všetkých uzloch matice. Vstup synchronizácie spúšťača a jeho výstup do dátovej linky spoločnej pre túto maticu sú zapojené tak, ako je znázornené na obrázku 7, a.

Je zrejmé, že iba klopný obvod bude fungovať, ak vstupy prvku AND z riadku DC a stĺpca DC dostanú 1.

V našom prípade sa vyberie zakrúžkovaný maticový prvok (obrázok 7, b).

1.5 Princíp zápisu/čítania informácií

Prvok matice inicializujeme odoslaním adresy na adresové vstupy. Teraz si ukážeme, ako bude prebiehať proces zápisu/čítania dát. Všimnite si, že každá matica má jeden spoločný dátový vodič, t.j. Každý bit údajov je zaznamenaný vo svojej vlastnej matici. Adresovanie takýchto matíc sa vykonáva paralelne.

Uvažujme o prístupe k jednému bitu údajov. Len keď je úroveň CS 0 aplikovaná na vstup (obr. 8), môže sa na výstupe riadiacich obvodov čítacej a zapisovacej vyrovnávacej pamäte objaviť 1. Navyše na výstupe riadenia zapisovacej vyrovnávacej pamäte sa objaví 1, keď je 0 na vstupe. a na výstupe riadenia čítacej vyrovnávacej pamäte - keď je 1 zapnutá.

Obrázok 8 – Funkcie CS a vstupov

1.6 Konštrukcia pamäťového priestoru danej veľkosti

Na vytvorenie pamäte ľubovoľnej veľkosti je možné použiť čipy SRAM s malou kapacitou. Predpokladajme, že máme čipy SRAM s kapacitou 256x4. Je potrebné vytvoriť pamäť zariadenia s kapacitou 1 KB alebo 1K × 8. Obvod 256×4 má 4 matice po 256 buniek (256 = 2 8), t.j. obvod má 8 adresovateľných vstupov.

Obrázok 9 – Pamäťový čip 256×4

Aby ste zabezpečili čítanie/zápis bajtu informácie, musíte pridať ďalšie 4 matice pomocou externého pripojenia (t.j. spojiť 2 čipy).

Získame ekvivalentný obvod, ktorý umožňuje uložiť 256 bajtov informácií.

Na vybudovanie 1 KB pamäte potrebujete 4 z nasledujúcich obvodov:

1K = 210; 2 10 / 2 8 = 2 2 = 4.

Obrázok 10 – Získanie ekvivalentného obvodu 256×8

Prístup k takejto pamäti sa vykonáva cez 10 adresných riadkov (1K = 2 10): 8 adresných riadkov je pripojených priamo k obvodu a 2 sú pripojené k dekodéru, pomocou ktorého sa volí jeden zo 4 smerov.

Všeobecný pamäťový obvod (obrázok 11) je tvorený ekvivalentnými obvodmi (obrázok 10), pôvodný mikroobvod je znázornený na obrázku 9.

Obrázok 11 – Schéma 1Kbyte statickej pamäte

2.1 Praktická časť

Zostavte vnútornú pamäť procesorového systému pozostávajúcu z ROM a statickej RAM. Procesorový systém pracuje v reálnom režime.

Bitová kapacita ША - 20, ШД - 8.

|

od 00000 do 03FFF |

od 80 000 do 9 FFFF |

Určenie kapacity ROM a RAM

Na základe získaného rozsahu adries určíme kapacitu ROM a RAM.

Určme počet meniacich sa bitov a napíšme adresu v binárnom kóde.

ROM 00000 až 03FFF

Počiatočná adresa: 00000000000000000000 2 .

Konečná adresa: 0000001111111111111 2 .

Zmenilo sa 14 bitov, čo znamená, že kapacita ROM je 2 14.

Pre 8-bitovú dátovú zbernicu, kapacita ROM 2 14 *8:

2 14 = 2 10 *2 4 ,

2 10 = 1K - kilobajt, takže kapacita ROM je 16K*8.

RAM od 80 000 do 9 FFFF

Počiatočná adresa: 10000000000000000000 2 .

Konečná adresa: 10011111111111111111 2 .

Zmenilo sa 17 číslic.

Pre 8-bitovú dátovú zbernicu je kapacita RAM:

2 17 = 2 10 *2 7

2 10 = 1K - kilobajt, takže kapacita RAM je 128K*8.

Na zobrazenie obvodu je potrebné určiť kapacity čipov RAM a ROM. ROM má kapacitu 16K*8 (obr. 1) a RAM má kapacitu 64K*4 (obr. 2), obvod ROM má teda 14 adresových vstupov 16K = 2 14, osem dátových vstupov/výstupov. a CS vstup (vzorky čipu). Obvod RAM má 17 adresových vstupov 128K= 2 17, štyri dátové vstupy/výstupy, CS a

Obrázok 1 - ROM čip 16K*8

Obrázok 2 - 64K*4 čip RAM

štruktúra ROM

Kapacita ROM - 16K*8. Kapacita mikroobvodu je 16K*8, čo znamená, že pre získanie požadovanej kapacity ROM zostavte jeden mikroobvod (obr. 3).

Obrázok 3 - Štruktúra ROM 16K*8

Štruktúra RAM

Kapacita RAM je 128K*8, kapacita mikroobvodu je 64K*4, čo znamená, že na zostavenie takejto RAM je potrebné postaviť 2 mikroobvody.

Obrázok 4 - Štruktúra RAM 128K*8

Všeobecná štruktúra pamäte

Podľa pokynov sú počiatočné adresy ROM a RAM nasledovné:

ROM (00000 – 000000000000000000000 2),

RAM (80000 – 10000000000000000000 2).

Podľa stavu bitov: A19, A18 - 00 funguje ROM a podľa stavu A19, A18 - 01 funguje RAM. Pomocou jednoduchej logiky môžete

postaviť smerový dekodér ROM/RAM (obr. 5).

Obrázok 5 - Smerový dekodér ROM-RAM

Obrázok 6 - Všeobecná štruktúra projektovanej pamäte

Záver

V tejto práci na kurze bola vykonaná úloha vyvinúť blok vnútornej pamäte procesorového systému pozostávajúceho z ROM a statickej pamäte RAM. Všetky potrebné komponenty a prvky boli popísané v analytickej, štrukturálnej a grafickej forme.

Pri výpočte tejto práce v kurze boli použité matematické a grafické balíky, ako napríklad:

Bibliografia

1 Ugryumov E.P. Digitálne obvody. Petrohrad: BHV-SPb, 2000.

2 Veľké integrované pamäťové čipy: referenčná kniha. M.: Rádio a komunikácia, 1990.