Характеристики spd что. SPD-Z - фирменная утилита для работы с SPD оперативной памяти OCZ или лапша? Что такое память DDR3

Это модуль, функцией которого является хранение данных и предоставление их по требованию устройству или программе - по сути это посредник между процессором и дисковыми накопителями. RAM является энергозависимым устройством, т.е. может работать лишь пока на него подается питание, при отключении которого все данные теряются. Разберемся более подробно в характеристиках этого важнейшего устройства, без которого ваш ПК, смартфон, ноутбук или планшет будет обычной грудой железа.

Типы ОЗУ

RAM бывают нескольких типов, кардинально отличающихся характеристиками и архитектурой.

– синхронная динамическая память с произвольным доступом. Раньше была довольно популярной и использовалась почти во всех компьютерах, благодаря наличию синхронизации с системным генератором, который, в свою очередь, позволял контроллеру очень точно определять время, когда данные будут готовы. В итоге значительно уменьшилось время задержек по циклам ожидания в связи с доступностью данных на каждом такте таймера. Сегодня вытеснена более современными типами памяти.

– это динамическая синхронизированная память, в ее основе лежит принцип случайного доступа и двойная скорость обмена данными. Такой модуль обладает рядом положительных характеристик относительно SDRAM, важнейшая из которых – за 1 такт системного генератора осуществляется 2 операции, то есть при неизменной частоте пропускная способность на пике увеличивается в 2 раза.

– это следующая разработка, работает так же, как и у ОЗУ типа DDR, отличительная особенность данной модели заключается в удвоенной по объему выборке данных на такт (4 бита вместо 2х). Кроме того второе поколение стало более энергоэффективным, уменьшилось тепловыделение, а частоты выросли.

– новое поколение RAM, важнейшая отличительная особенность от DDR2 – выросшие частоты и уменьшенное потребление энергии. Также совершенно изменена конструкция ключей (специальные прорези для точного вхождения в слот).

Существуют модификации DDR3, отличающиеся еще меньшим потреблением энергии - DDR3L и LPDDR3 (напряжение у первой модели уменьшено до 1.35 В, а у второй до 1.2 В, тогда как у простых DDR3 оно равно 1.5В).

DDR4 SDRAM

- новейшее поколение оперативной памяти. Характеризуется выросшей до 3,2 Гбит/с скоростью обмена данными, увеличенной до 4266 МГц частотой и значительно улучшенной стабильностью.

RIMM (RDRAM, Rambus DRAM) – память, основанная на тех же принципах, что и DDR, но с повышенным уровнем тактовой частоты, что было достигнуто за счет меньшей разрядности шины. Также при адресации ячейки номера строки и столбца предаются одновременно.

Стоимость RIMM была намного выше, а производительность лишь немногим превышала DDR, в итоге RAM этого типа просуществовали на рынке недолго.

Выбирайте тип RAM не только исходя из потенциала и характеристик вашей материнской платы, но и учитывая совместимость с другими составляющими системы.

Варианты физического расположения чипов (упаковка)

Устанавливаемые на модули ОЗУ чипы памяти располагаются либо с одной стороны (одностороннее месторасположение), либо с двух (двустороннее). В последнем варианте модули получаются достаточно толстыми, что не позволяет установить их на отдельные ПК.

Форм-фактор это

Специально разработанный стандарт в котором описаны размеры модуля ОЗУ, общее количество и месторасположение контактов. Существует несколько типов форм-факторов:

SIMM

(Single in Line Memory Module) - 30 или 72 двухсторонних контакта;

RIMM – фирменный форм-фактор модулей RIMM (RDRAM). 184, 168 или 242 контакта;

DIMM

(Dual in Line Memory Module) – 168, 184, 200 или 240 независимых, расположенных по обеим сторонам модуля, контактных площадок.

FB-DIMM (Fully Buffered DIMM) – исключительно серверные модули. Идентичны по форм-фактору DIMM с 240 контактами, но используют лишь 96, за счет последовательного интерфейса. Благодаря присутствующей на каждом модуле микросхеме AMB (Advanced Memory Buffer) обеспечивается высокоскоростная буферизация и конверсия всех сигналов, в том числе и адресации. Также значительно улучшены производительность и масштабируемость. Совместимы только с аналогичной полностью буферизованной памятью.

LRDIMM

(Load Reduced Dual In-Line Memory Modules) – исключительно серверные модули. Оснащаются буфером iMB (Isolation Memory Buffer), снижающим нагрузку на шину памяти. Применяются для ускорения работы больших объемов памяти.

SODIMM

(Small Outline Dual In-Line Memory Module) – подвид DIMM с меньшими размерами для установки в портативные устройства, в основном - ноутбуки. 144 и 200 контактов, в более редком варианте - 72 и 168.

MicroDIMM (Micro Dual In-Line Memory Module) - еще уменьшенный SODIMM. Обычно имеют 60 контактов. Возможные реализации контактов - 144 SDRAM, 172 DDR и 214 DDR2.

Отдельного упоминания заслуживает низкопрофильная (Low Profile) память - созданные специально для невысоких серверных корпусов модули с меньшей, по сравнению со стандартными, высотой.

Форм-фактор является основным параметром совместимости RAM с материнской платой, поскольку при его несовпадении модуль памяти элементарно не получится вставить в слот.

Что такое SPD?

На каждой планке форм-фактора DIMM имеется маленький чип SPD (Serial Presence Detect), в котором зашиты данные о параметрах физических чипов. Данная информация имеет критическое значение для бесперебойной работы и считывается BIOS на этапе теста для оптимизации параметров доступа к ОЗУ.

Ранки модуля памяти и их количество

Блок памяти шириной 64 бита (72 для модулей с ECC), образованный N физическими чипами. Каждый модуль может иметь от 1 до 4 ранков, причем свое ограничение на количество ранков существует и у материнских плат. Поясним - если на материнскую плату может быть установлено не более 8 ранков, то это значит что суммарное количество ранков модулей RAM не может превышать 8, например, в данном случае - 8 одноранковых или 4 двухранковых. В независимости от того остались ли еще свободные слоты - при исчерпанном лимите ранков дополнительные модули будет установить невозможно.

Определить ранк для конкретного ОЗУ довольно просто. У компании Kingston количество ранков определяется одной из 3-х букв в центре маркировочного списка: S – это одноранговая, D – друхранговая, Q – четырехранговая. Например:

- KVR1333D3LS 4R9S/4GEC

- KVR1333D3LD 4R9S/8GEC

- KVR1333D3LQ 8R9S/8GEC

Прочие же производители указывают этот параметр как, например, 2Rx8, что означает:

2R - двухранковый модуль

x8 - ширина шины данных на каждом чипе

т.е. модуль 2Rx8 без ECC имеет 16 физических чипов (64х2/8).

Тайминги и латентность

Выполнение любой операции чипом памяти происходит за определенное число тактов системной шины. Требуемые для записи и считывания данных количества тактов и есть тайминги.

Латентность, если коротко - задержка обращения к страницам памяти, также измеряется в количестве циклов и записывается 3-я числовыми параметрами: CAS Latency, RAS to CAS Delay, RAS Precharge Time. Иногда добавляется четвертая цифра - «DRAM Cycle Time Tras/Trc», характеризующая общее быстродействие всей микросхемы памяти.

CAS Latency или CAS

(CL) – ожидание от момента, когда данные были запрошены процессором и до начала их считывания с RAM. Одна из важнейших характеристик определяющих скорость работы ОЗУ. Маленькое CL говорит о высоком быстродействии RAM.

RAS to CAS Delay (tRCD) - задержка между передачей сигнала RAS (Row Address Strobe) и CAS (Column Address Strobe), необходимая для четкого отделения этих сигналов контроллером памяти. Проще говоря - запрос на чтение данных включает в себя номера строки и столбца страницы памяти и эти сигналы должны быть отчетливыми, в противном случае будут возникать множественные ошибки данных.

RAS Precharge Time (tRP) - определяет время задержки между деактивацией текущей строки данных и активацией новой. Иначе говоря – интервал, спустя который контроллер может снова подать сигналы RAS и CAS.

Тактовая частота, частота передачи данных (Data rate)

Частота передачи данных (Иначе - скорость передачи данных) - максимально возможное число циклов передачи данных в секунду. Измеряется в гигатрансферах (GT/s) или мегатрансферах (MT/s).

Тактовая же частота определяет максимальную частоту системного генератора. Надо помнить, что DDR расшифровывается как Double Data Rate, что означает удвоенную частоту обмена данными относительно тактовой. Так, например для модуля DDD2-800 тактовая частота будет 400.

Пропускная способность (пиковая скорость передачи данных)

В упрощенном варианте рассчитывается как частота системной шины умноженная на передаваемый за такт объем данных.

Пиковая же скорость является произведением частоты и разрядности шины на количество каналов памяти (Ч×Р×К). На модуле памяти указывается как, например, PC3200, что, очевидно, означает - пиковая скорость передачи данных для этого модуля равна 3200 Мбайт/с.

Для оптимальной работы системы суммарное значение ПСПД планок памяти не должно превышать ПС шины процессора, исключением является двухканальный режим, когда планки будут занимать шину по очереди.

Что такое поддержка ЕСС (Error Correct Code)

Память с поддержкой ECC позволяет находить и исправлять спонтанные ошибки во время передачи данных. Физически ECC исполнена в виде дополнительного 8-разрядного чипа памяти на каждые 8 основных и представляет собой значительно улучшенный "контроль четности". Суть данной технологии состоит в отслеживании одного произвольно измененного в процессе записи/считывания 64-битного машинного слова бита с последующим его исправлением.

Буферизованная (регистровая) память

Характеризуется наличием на модуле RAM специальных регистров (буферов), обрабатывающих сигналы управления и адресации от контроллера. Несмотря на возникающий благодаря буферу дополнительный такт задержки, регистровая память тем не менее широко используется в профессиональных системах из-за пониженной нагрузки на систему синхронизации и значительно повышенной надежности.

Надо помнить, что буферизированная и небуферизированная память являются несовместимыми и не могут работать в одном устройстве.

Память: ОЗУ, DDR SDRAM, SDR SDRAM, PC100, DDR333, PC3200... как во всём этом разобраться? Давайте попробуем!

Итак, первое что мы должны сделать это "разгладить" все сомнения и вопросы по поводу номиналов на памяти...

Самые распространённые типы памяти это:

- SDR SDRAM (обозначения PC66, PC100, PC133)

- DDR SDRAM (обозначения PC266, PC333 и т.д. или PC2100, PC2700)

- RDRAM (PC800)

Теперь для последующих объяснений, расскажу про тайминги и частоты. Тайминг - это задержка между отдельными операциями, производимыми контроллером при обращении к памяти.

Если рассмотреть состав памяти, получим: всё её пространство представлено в виде ячеек (прямоугольники), которые состоят из определённого количества строк и столбцов. Один такой "прямоугольник" называется страницей, а совокупность страниц называется банком.

Для обращения к ячейке, контроллер задаёт номер банка, номер страницы в нём, номер строки и номер столбца, на все запросы тратится время, помимо этого довольно большая затрата уходит на открытие и закрытие банка после самой операции чтения/записи. На каждое действие требуется время, оно и называется таймингом.

Теперь рассмотрим поподробнее каждый из таймингов. Некоторые из них не доступны для настройки - время доступа CS# (crystal select ) этот сигнал определяет кристалл (чип) на модуле для проведения операции.

Кроме этого, остальные можно менять:

- RCD (RAS-to-CAS Delay) это задержка между сигналами RAS (Row Address Strobe) и CAS (Column Address Strobe) , данный параметр характеризует интервал между доступами на шину контроллером памяти сигналов RAS# и CAS# .

- CAS Latency (CL) это задержка между командой чтения и доступностью к чтению первого слова. Введена для набора адресными регистрами гарантированно устойчивого уровня сигнала.

- RAS Precharge (RP) это время повторной выдачи (период накопления заряда) сигнала RAS# - через какое время контроллер памяти будет способен снова выдать сигнал инициализации адреса строки.

- Precharge Delay (или Active Precharge Delay ; чаще обозначается как Tras ) это время активности строки. Т.е. период, в течение которого закрывается строка, если следующая требуемая ячейка находится в другой строке.

- SDRAM Idle Timer (или SDRAM Idle Cycle Limit ) количество тактов, в течение которых страница остаётся открытой, после этого страница принудительно закрывается, либо для доступа к другой странице, либо для обновления (refresh)

- Burst Length это параметр, который устанавливает размер предвыборки памяти относительно начального адреса обращения. Чем больше его размер, тем выше производительность памяти.

Примечание:

порядок операций именно таков (RCD-CL-RP), но зачастую тайминги записывают не по порядку, а по "важности" - CL-RCD-RP.

Ну вот, вроде разобрались с основными понятиями о таймингах, теперь рассмотрим подробнее номиналы памяти (PC100, PC2100, DDR333 и т.д.)

Существует два типа обозначений для одной и той же памяти: одно - по "эффективной частоте" DDRxxx, а второе - по теоретической пропускной способности PCxxxx.

Обозначение "DDRxxx" исторически развилось из последовательности названий стандартов "PC66-PC100-PC133" - когда было принято скорость памяти ассоциировать с частотой (разве что ввели новое сокращение "DDR" для того, чтобы отличать SDR SDRAM от DDR SDRAM). Одновременно с памятью DDR SDRAM появилась память RDRAM (Rambus), на которой хитрые маркетологи решили ставить не частоту, а пропускную способность - PC800. При этом ширина шины данных как была 64 бита (8 байт) - так и осталась, то есть те самые PC800 (800 МБ/с) получались умножением 100 МГц на 8. Естественно от названия ничего не поменялось, и PC800 RDRAM - суть та же самая PC100 SDRAM, только в другом корпусе... Это ничего больше, чем стратегия для продаж, грубо говоря "наколоть людей". В ответ компании, которые выпускают модули, стали писать теоретическую пропускную способность - PCxxxx. Так появились PC1600, PC2100 и следующие... При этом у DDR SDRAM эффективная частота выше в два раза, а значит и больше числа на обозначениях.

Вот пример соответствий обозначений:

- 100 МГц = PC1600 DDR SDRAM = DDR200 SDRAM = PC100 SDRAM = PC800 RDRAM

- 133 МГц = PC2100 DDR SDRAM = DDR266 SDRAM = PC133 SDRAM = PC1066 RDRAM

- 166 МГц = PC2700 DDR SDRAM = DDR333 SDRAM = PC166 SDRAM = PC1333 RDRAM

- 200 МГц = PC3200 DDR SDRAM = DDR400 SDRAM = PC200 SDRAM = PC1600 RDRAM

- 250 МГц = PC4000 DDR SDRAM = DDR500 SDRAM

Что же касается RAMBUS (RDRAM) писать много не буду, но всё же постараюсь ее вам представить.

Существует три разновидности RDRAM - Base , Concurrent и Direct . Base и Concurrent это практически одно и тоже, но Direct имеет приличные отличия, поэтому расскажу про первые две обобщённо, а про последнюю - поподробней.

Base RDRAM и Concurrent RDRAM в основном отличаются только рабочими частотами: для первой частота составляет 250-300 MHz, а для второй этот параметр, соответственно, равен 300-350 MHz. Данные передаются по два пакета данных за такт, так что эффективная частота передачи получается в два раза больше. Память использует восьми битную шину данных, что, следовательно, дает пропускную способность 500-600 Mb/s (BRDRAM) и 600-700 Mb/s (CRDRAM).

Direct RDRAM (DRDRAM) в отличие от Base и Concurrent, имеет 16-битную шину и работает на частоте 400 MHz. Пропускная способность Direct RDRAM составляет 1.6 Gb/s (учитывая двунаправленную передачу данных), что уже по сравнению с SDRAM (1 Gb/s для РС133) выглядит довольно неплохо. Обычно, говоря о RDRAM, подразумевают DRDRAM, поэтому буква "D" в названии часто опускается. При появлении этого типа памяти Intel создала чипсет для Pentium 4 - i850.

Самый большой плюс Rambus памяти это то, что чем больше модулей - тем больше пропускная способность, например до 1.6 Gb/s на один канал и до 6.4 Gb/s при четырех каналах.

Имеется также два недостатка, довольно значительных:

1. Лапки золотые и приходят в негодность, если плату памяти вытащить и вставить в слот больше 10 раз (примерно).

2. Завышенная цена, но многие находят очень хорошее применение этой памяти и готовы заплатить за них большие деньги.

Вот, пожалуй, и всё, мы разобрались с таймингами, названиями и номиналами, теперь я расскажу немного о различных немаловажных мелочах.

Вы наверняка видели в BIOS"e при настройках частоты памяти опцию By SPD что это значит? SPD - Serial Presence Detect , это микросхема на модуле, в которую зашиты все параметры для работы модуля, это так сказать "значения по умолчанию". Сейчас из-за появления "noname" компаний, стали записывать в этот чип имя производителя и дату.

Регистровая память

Registered Memory это память с регистрами, которые служат буфером между контроллером памяти и чипами модуля. Регистры уменьшают нагрузку на систему синхронизации и позволяют набирать очень большое количество памяти (16 или 24 гигабайт) не перегружая цепи контроллера.

Но данная схема имеет недостаток - регистры вносят задержку в 1 такт на каждую операцию, а значит - регистровая память медленнее обычной при прочих равных условиях. То есть - оверклокеру неинтересна (да и стОит она очень дорого).

Все сейчас кричат про Dual channel - что это?

Dual channel - двойной канал, это позволяет обращаться одновременно к двум модулям. Dual channel - это не тип модулей, а функция интегрированная в материнскую плату. Может быть задействована с двумя (желательно) идентичными модулями. Включается он автоматически при наличие 2-х модулей.

Примечание: чтобы активировать эту функцию, надо установить модули в слоты разных цветов.

Parity и ECC

Memory with Parity это память с проверкой чётности, способна детектировать некоторые типы ошибок.

Memory with ECC это память с коррекцией ошибок, позволяет найти, а также исправить ошибку одного бита в байте. Применяется в основном на серверах.

Примечание: она медленнее обычной, не годится для людей любящих скорость.

Надеюсь, после прочтения статьи вы разобрались с более популярными "непонятными понятиями".

Что такое SPD (Serial Presence Detect)?

Все

современные модули памяти имеют в своем

составе микросхему SPD (Serial Presence Detect).

Интерфейс последовательного детектирования

использует шину управления системой

(SMBus - System Management Bus), посредством которой

простые микросхемы могут общаться с

остальной частью системы. В 1997 году

SMBus был объединен с другим расширенным

интерфейсом - ACPI (Advanced Configuration and Power

Interface), став его неотъемлемой частью.

Принцип

использования SPD сводится к передаче

данных (при помощи системного BIOS) от

микросхемы EEPROM, установленной на модуле,

соответствующим регистрам контроллера

памяти, находящегося в составе северного

моста, через SMBus-интерфейс объединенного

контроллера периферийных компонент

(южный мост, или концентратор контроллеров

ввода/вывода - см. рис. 1). Таким образом,

система получает все необходимые данные

о модуле и настраивается на оптимальный

режим работы, согласно записанным в

микросхему SPD значениям.

Общий

стандарт SPD (JEDEC Standard No. 21-С, часть 4.1.2)

определен на уровне объединенного

совета разработчиков электронных

устройств (JEDEC - Joint Electronic Device Engineering

Council) и предусматривает единую байтовую

карту программирования в шестнадцатиричном

(HEX) коде, где размещаются данные общим

объемом 2048bit (или 256 байтовых полей) - это

сделано с целью создать общий стандарт

записи основной информации, всесторонне

классифицирующей определенный модуль

памяти (табл. 1).

Все

модули, поддерживающие схему

последовательного детектирования,

должны в обязательном порядке обеспечивать

операции записи страницы как минимум

четырех последовательных адресов. Сама

схема SPD характеризуется интерфейсным

протоколом, размером карты программирования,

типом используемых данных и содержанием.

Рис.

1.

Считывание/запись

данных из/в EEPROM производится по линии

ввода/вывода SDA при помощи сигнала SCL

(входящий сигнал синхронизации

чтения/записи данных) совместно с

сигналами адреса SA, предусмотренных

цоколевкой модуля (рис.2). Система

синхронизируется с микросхемой SPD на

частоте 80kHz.

Рис. 2.

Таблица 1

Карта SPD должна программироваться один раз и больше никогда не меняться - по требованиям основного стандарта после внесения данных в EEPROM, вход WP (Write Protect) устанавливается в положение "non-write" для исключения возможности случайного стирания или умышленной замены содержимого микросхемы. В общем случае вывод WP микросхемы EEPROM, отвечающий за защиту от записи, соединяется с сигнальной линией SWP модуля, на которой уровень сигнала активный высокий по умолчанию (в случае низкого уровня микросхема открыта для записи). Линии SDA и SCL имеют схему включения типа "открытый сток" (Open-drain) или "открытый коллектор" (Open-collector), и требуют внешней подтягивающей нагрузки 47 кОм. Ток утечки источника этих линий должен быть как минимум 3mA, чтобы поддерживать действительный низкий уровень сигнала Стандарт JEDEC Std No. 21-C-4.1.2 регламентирует применение схемы последовательного детектирования в любых модулях памяти независимо от типа применяемого ОЗУ/ПЗУ и форм-фактора. Это придает данной схеме исключительную гибкость и универсальность, поскольку стандарт предусмотрен для настоящих и последующих архитектур, и включает резервные поля для внесения специальной информации, которая потребуется в будущем. Когда стандартизируется специфическая архитектура, отличная от базовой, предусматривающая собственные особенности функционирования, специфическую организацию, индивидуальные характеристики и т.д. - все отражается в схеме SPD: отличия заносятся в резервные биты (если таких характеристик не предусмотрено в текущей), а в общей спецификации описывается соответствующим дополнением, кроме чего, на каждую отдельную характеристику должна присутствовать адресная карта. Общая схема назначения адресных байт SPD SIMM/DIMM приведена в табл. 1.

Все

модули памяти, имеющие разный форм-фактор,

содержащие память со своими архитектурными

особенностями, и в которых применяется

схема последовательного детектирования,

должны отвечать следующим требованиям:

-

известный интерфейсный протокол;

-

подходящая (приемлемая) конфигурация

модуля;

-стандартизированная

архитектура ("глубина", "ширина",

количество используемых банков, схема

адресации и т.д.);

-

поддерживаемая схема проверки ошибок

(ECC, Parity и т.д.);

-

стандартная или одобренная комиссией

"проводная диаграмма" (монтаж и

разводка сигнальных трасс на модуле

памяти).

Наличие

схемы последовательного детектирования

на модуле памяти избавляет производителей

материнских плат от необходимости

вносить оптимальные значения основных

временных параметров в системный BIOS,

поскольку вся необходимая информация

для нормальной настройки подсистемы и

ее стабильного функционирования

содержится в микросхеме SPD. Кроме этого,

механизм SPD может настроить систему и

гарантировать устойчивую работу при

использовании в подсистеме памяти

модулей разной организации, разного

объема и имеющих разные значения

одноименных параметров (при инициализации

системы будут считаны записанные в SPD

модуля памяти данные). Перезапись

микросхем EEPROM имеет смысл лишь при

исправлении дефектов в записанной

информации

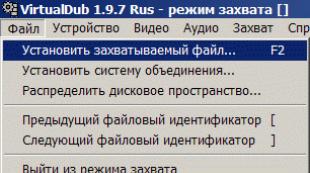

Компания OCZ, известный производитель компьютерных комплектующих для энтузиастов, решила попробовать разрекламировать себя при помощи вспомогательных приложений. На официальном форуме была анонсирована хитрая утилита под названием SPD-Z. Как не трудно догадаться по аббревиатуре, предназначена она для работы со служебной информацией модулей оперативной памяти. Стоить отметить, что до сего момент ни один из производителей подобного рода не выпускал для свободного использования утилиты, которые могут принести вред аппаратным компонентам в случае некорректного использования.

Для неподготовленных пользователей даже был написан специальный алгоритм работы утилиты, по которому можно легко себе представить, что же на самом деле делает программа.

реклама

Разработчики позиционируют продукт все для той же категории энтузиастов. Утилита же позволяет перепрошивать тайминги памяти только на модулях вышеупомянутого производителя. Говорится о том, что подобные манипуляции могут привести к улучшенной производительности и корректной совместимости в некоторых случаях. Программа проверяет номер партии чипов, и автоматически отправляется на сервер с архивом совместимых профилей. Все что должен сделать пользователь, это убедиться в том, что система не разогнана и стабильна на все 100% (правда непонятно о повышении какой совместимости идет речь?).

Категорически не рекомендуется ставить эксперименты на основном

рабочем компьютере, лучше найти какую-нибудь старую плату, оставшуюся, например,

с прошлого апгрейда или частично исправную и собрать на ее базе "полигон".

Об аппаратной защите и ее эффективности

Микросхема 24C02 поддерживает аппаратную

защиту записи. Для этого используется вход WP (Write Protect). Это контакт 7 на

8-контактном корпусе микросхемы. При WP=0 запись разрешена, при WP=1 запрещена.

С точки зрения использования этой функции, модули памяти бывают трех типов:

Первый вариант – вход WP подключен к схемной "земле", то есть WP=0. Защиты нет.

Второй вариант

– вход WP подключен к плюсовой линии питания, то есть WP=1. При

этом микросхема SPD постоянно защищена от записи, и программно изменить ее

содержимое невозможно.

Третий вариант

– вход WP подключен к соответствующему контакту на разъеме DIMM.

При этом наличие защиты записи будет зависеть от материнской платы, а именно от

того, какой логический уровень подает она на данный контакт. Обычно подается

постоянный уровень "0" или "1", что обеспечивает разрешение или запрет записи

соответственно. Теоретически, на материнской плате может быть реализован

программно-доступный регистр, через который можно управлять состоянием этой

линии, то есть программно устанавливать и снимать защиту записи SPD. Но на

практике такие решения встречаются крайне редко.

Тем, кто решит поэкспериментировать с перезаписью SPD, необходимо проверить

наличие логического "0" на контакте 7 микросхемы 24C02 и при необходимости

внести изменения в схему. Описание этой микросхемы приведено в .

Расположение сигналов на разъеме DIMM для разных типов памяти приведено в

.

Другой тип защиты – отключение сигналов шины SMBus с помощью

программно-управляемых коммутаторов. Смысл такой защиты в том, что для

управления указанными коммутаторами используются специфические ресурсы

материнской платы, не являющиеся частью чипсета. Поэтому для ответа на вопрос,

что и в какой регистр нужно записать для выключения защиты, документации на

чипсет недостаточно, требуется принципиальная электрическая схема данной

материнской платы, которая обычно недоступна. На практике этот тип защиты

используется достаточно редко. Автор встречал его только в некоторых моделях

плат производства фирмы ASUS.

Таким образом, в большинстве платформ, защищенность информации SPD от

программного искажения зависит только от подключения входа WP микросхемы 24C02

на модуле DIMM.

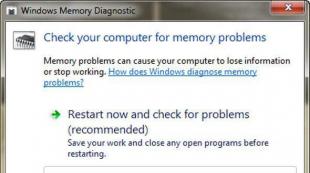

Симптомы неисправности

Разумеется, содержимое микросхемы SPD модуля памяти может быть искажено не

только в результате действия вредоносных программ. Причиной может быть

программный сбой, а также аппаратная неисправность самой микросхемы SPD или

контроллера SMBus.

Симптомы такой неисправности существенно различаются в зависимости от двух

факторов: типа платформы и характера искажения (какие именно параметры

искажены).

В "древних" платформах, использующих память PC66, PC100, PC133 SDRAM, несмотря

на то, что модули DIMM уже содержали SPD, разработчики BIOS в силу определенной

инерционности использовали "старые" методы детектирования памяти, основанные на

записи в ОЗУ тестовых данных и их контрольном считывании по специальному

алгоритму без использования SPD. В таких платформах искаженность содержимого

микросхемы SPD и даже ее физическое снятие с модуля DIMM, в большинстве случаев

не приводит к потере работоспособности, хотя контроллер памяти может быть

проинициализирован неоптимально.

Используя данное свойство "древних" платформ автор успешно применял плату на

чипсете Intel BX в качестве программатора для микросхем 24C02, временно

устанавливая микросхему, которую требуется записать, на один из модулей памяти,

вместо микросхемы SPD.

В более новых платформах, использующих DDR, DDR2, DDR3, процедура настройки

контроллера памяти значительно сложнее и выполнить ее без привлечения информации

из SPD невозможно. Такие платы обычно не стартуют, если присутствует хотя бы

один модуль DIMM с некорректным содержимым SPD. Даже если этот модуль установлен

в старшем банке, а в младшем находится исправный модуль.

Разумеется, многое зависит и от того какой параметр искажен. Например, если

увеличено значение байта, задающего тактовый период, BIOS будет устанавливать

пониженную частоту при инициализации контроллера памяти, что приведет к падению

быстродействия.

Отметим, что данные SPD защищены контрольной суммой, поэтому вредоносная

программа, желающая изменить тайминги модуля памяти без вывода его из строя,

должна корректировать значение контрольной суммы после изменения значений

параметров. Также отметим, что на некоторых материнских платах BIOS не

проверяет контрольную сумму SPD. Поэтому модуль памяти с работоспособными

значениями параметров, но некорректной контрольной суммой SPD, может нормально

работать на таких платах.

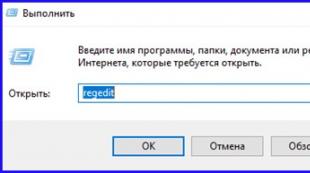

Меры предосторожности

Тем, кто решится поэкспериментировать с перезаписью микросхем SPD, следует

заранее позаботиться о восстановлении их содержимого. Исходное содержимое SPD

всех модулей памяти следует предварительно сохранить в файлах с помощью

программы чтения SPD, имеющейся в предлагаемом наборе. Категорически не

рекомендуется ставить такие эксперименты на основном рабочем компьютере, лучше

найти какую-нибудь старую плату, оставшуюся, например, с прошлого апгрейда или

частично исправную и собрать на ее базе "полигон".

Оптимально, если это будет плата на чипсетах, например Intel TX, LX, BX,

использующая SDRAM первого поколения. Как было сказано выше, такие платы обычно

сохраняют работоспособность при некорректном содержимом SPD, поэтому вероятность

получить нестартующую систему будет ниже.

Напомним, что BIOS считывает SPD только при перезапуске компьютера, поэтому,

делая опыты по перезаписи SPD, по возможности восстанавливайте исходное

содержимое перед сбросом или выключением питания.

Программа чтения SPD (каталог WORK\READ)

Как и в ранее опубликованных статьях данного цикла, в целях монопольного и

беспрепятственного взаимодействия программы с оборудованием при работе с

предлагаемыми примерами, автор применил "древнюю" технологию отладки под DOS.

Аргументация такого шага и рекомендации по организации рабочего места приведены

в ранее опубликованной статье " ".

Программа считывает содержимое SPD заданного модуля памяти (номер модуля

запрашивается) и сохраняет его в двоичном файле SPD.BIN, размером 256 байт. В

текущей версии поддерживаются чипсеты:

Intel от 430TX до 945 (c "южными мостами" PIIX4, ICH0-ICH7).

VIA от MVP3 до К8x (с "южными мостами" VT82C586B, VT82C596A/B, VT82C686A/B,

VT8233, VT8235, VT8237).

Поддержка чипсетов NVidia, SiS, ATI планируется в последующих реализациях

программы. При наличии читательского интереса автор вернется к данной теме.

Каталог содержит следующие файлы:

ASM_TD.BAT

– обеспечивает ассемблирование, линковку и запуск программы под

отладчиком. При запуске TASM и TLINK используются опции, обеспечивающие

добавление отладочной информации в EXE файл.

ASM_EXE.BAT – обеспечивает ассемблирование и линковку. Генерируется EXE файл.

RD_SPD.ASM – основной модуль программы.

A20.INC

– Библиотека для управления и контроля состояния адресной линии A20 с

использованием выходного порта контроллера клавиатуры.

BIGREAL.INC

– Библиотека поддержки режима Big Real Mode, для использования

32-битных адресов в диапазоне 0-4 Гб. Этот режим, как и управление адресной

линией A20, необходимы в данной программе только в том случае, когда чипсет

содержит конфигурационные регистры, находящиеся в пространстве памяти и для

включения контроллера SMB требуется перенастройка данных регистров (в том

случае, если BIOS запретил контроллер SMB перед загрузкой ОС). Такие регистры

имеются, например, в "южных мостах" Intel ICH6, ICH7. Это регистры memory-mapped

диапазона Root Complex Base Address – RCBA, подробности в .

SCREEN.INC

– Библиотека функций для вывода на экран в текстовом режиме 80x25

символов.

NUMPRINT.INC – Библиотека для вывода шестнадцатеричных чисел в текстовом виде.

PCIBIOS.INC

– Библиотека для доступа к конфигурационному пространству с

использованием функций PCIBIOS. Подробности в .

REFRDEL.INC

– Подпрограмма задержки, использующая Refresh Trigger. Подробности в

.

SMBUS.INC – Диспетчер функций для процедур поддержки System Management Bus.

SMBDEVS.INC

– Библиотека, обеспечивающая поддержку чипсетов. В этот модуль

вынесены подпрограммы, написанные под заданные чипсеты.

TEXT.INC – Текстовые строки.

CPU_DATA.INC

– Данные, используемые для управления адресной линией A20 и

включения режима Big Real Mode, обеспечивающего 32-битную адресацию.

SMB_DATA.INC

– Переменные и константы, используемые процедурами поддержки System

Management Bus.

Примечание 1.

Если файл с именем SPD.BIN уже существует, он будет перезаписан без

предупреждения.

Примечание 2.

В большинстве плат нумерация модулей памяти идет от центра платы. Например,

если на плате 4 разъема для DIMM, то у ближайшего к процессору разъема 3-битный

адрес микросхемы SPD будет 000b=0, у дальнего разъема 011b=3. Вместе с тем,

встречаются исключения, поэтому перед выполнением экспериментов следует

проверить нумерацию модулей. Это можно сделать с помощью диагностических утилит,

либо устанавливая один модуль поочередно во все разъемы и проверяя, при задании

какого номера DIMM программа его распознает.

Примечание 3.

В исходных текстах программы, наряду с процедурами чтения и записи байтов,

используемыми при операциях с микросхемами SPD (Read_Byte, Write_Byte),

содержатся также процедуры чтения и записи блоков (Read_Block, Write_Block). В

данной версии программы они не используются и резервируются для будущего

расширения функциональности. Процедуры блокового чтения и записи SMB потребуются

для взаимодействия с регистрами тактового генератора.

Программа записи SPD (каталог WORK\WRITE)

Программа считывает двоичный файл SPD.BIN, размером 256 байт и записывает его

содержимое в заданную микросхему SPD (номер модуля DIMM запрашивается).

Контрольная сумма автоматически корректируется.

Каталог содержит такой же набор файлов, что и каталог WORK\READ,

описанный выше.

Примечание 1.

Для плат с "южным мостом" VIA VT82C586B поддерживается только чтение SPD, без

записи. Это ограничение программы, не чипсета.

Примечание 2.

Программа записи SPD автоматически корректирует контрольную сумму данных.

Согласно стандарту, байт с адресом 3Fh должен содержать младшие 8 бит суммы

байтов с адресами 00h-3Eh. Если программа используется для модулей памяти,

использующих другой формат, либо требуется запрограммировать в микросхему

данные, не являющиеся информацией SPD, процедуру вычисления контрольной суммы

потребуется модифицировать.

Примечание 3.

На некоторых модулях памяти, в целях снижения стоимости, вместо микросхемы

24C02, допускающей перезапись, используется масочная микросхема постоянного

запоминающего устройства (ПЗУ), переписать содержимое которой невозможно.

Текстовые документы (каталог WORK\DOC).

README.TXT – краткая справка по использованию программ чтения и записи SPD.

SPD_SDR – описание формата SPD для модулей памяти SDRAM.

SPD_DDR – описание формата SPD для модулей памяти DDR SDRAM.

SPD_DDR2 – описание формата SPD для модулей памяти DDR2 SDRAM.

Документы в текстовом формате MS DOS. Перечисленные текстовые файлы могут быть

использованы как краткая русскоязычная справка по форматам SPD для различных

типов модулей памяти. Детальная информация содержится в .

Заключение

В статье рассмотрена одна из уязвимостей, которая может быть использована

вредоносными программами для выведения из строя оборудования, в частности

модулей памяти. Материал будет полезен при оценке степени защищенности систем и

выработке методов ее повышения. Для разбирающихся в схемотехнике и умеющих

держать в руках паяльник приведенных сведений будет вполне достаточно для

выполнения ремонта модулей DIMM у которых искажена информация SPD, а также

реализации программатора микросхем Serial Flash ROM на базе обычной материнской

платы.

Прилагаемые программы также будут полезны оверклокерам, для которых

редактирование содержимого SPD открывает новые возможности по "разгону" памяти,

так как набор параметров, которыми можно управлять, изменяя содержимое SPD,

существенно шире, чем набор опций BIOS Setup. Разумеется, действовать нужно

очень осторожно, заранее продумав пути восстановления работоспособности системы,

так как при записи некорректных параметров в SPD, обнуление CMOS уже не поможет.

Еще один вариант применения указанной технологии – хранение в неиспользуемой

области SPD "ключей", обеспечивающих, например, распознавание заданного

компьютера для защиты программ от несанкционированного копирования.

Источники информации

developer.intel.com .

1) Intel 82371AB PCI-TO-ISA / IDE XCELERATOR (PIIX4) Datasheet. Order Number

290562-001.

2) Intel 82801DB I/O Controller Hub 4 (ICH4) Datasheet. Document Number

290744-001.

3) Intel I/O Controller Hub 6 (ICH6) Family Datasheet. Document Number

301473-001.

Электронные документы, доступные на сайте

developer.amd.com .

4) AMD-8111 HyperTransport I/O Hub Data Sheet. Publication # 24674.

Электронные документы, доступные на сайте

datasheetarchive.com .

(Информация на данном сайте более полная, чем на "родных" сайтах

производителей указанных микросхем.)

5) VIA VT82C586B PIPC PCI Integrated Peripheral Controller. Для поиска

документа набирать строку "VT82C586B".

6) VIA VT82C686A South Bridge Datasheet. Revision 1.54. Для поиска документа

набирать строку "VT82C686".

7) VIA VT82C686B South Bridge Datasheet. Revision 1.71. Для поиска документа

набирать строку "VT82C686".

Электронные документы, доступные на сайте

pcisig.com .

Документы , на сайте pcisig.com доступны только для членов PCI

Special Interest Group. Воспользовавшись поисковыми системами, можно найти

данные документы для свободной загрузки.

8) PCI BIOS Specification. Revision 2.1.

9) PCI Local Bus Specification. Revision 3.0.

10) PCI-to-PCI Bridge Architecture Specification. Revision 1.1.

Электронные документы, доступные на сайте

smbus.org .

11) System Management Bus (SMBus) Specification. Version 2.0.

Электронные документы, доступные на сайте

semiconductors.philips.com .

12) The I2C-Bus Specification. Version 2.1.

Электронные документы, доступные на сайте

atmel.com .

13) AT24C01A/02/04/08/16 2-Wire Serial CMOS E2PROM Data Sheet.

Электронные документы, доступные на сайте

jedec.org .

14) JEDEC Standard No. 21-C. Page 4.1.2.5-1. Appendix E: Specific PD’s for

Synchronous DRAM (SDRAM).

15) JEDEC Standard No. 21-C. Page 4.1.2.4-1. Appendix D: DDR Synchronous DRAM

(DDR SDRAM). 16) JEDEC Standard No. 21-C Page 4.1.2.10-1. Appendix X: Serial

Presence Detects for DDR2 SDRAM (Revision 1.2).

17) JEDEC Standard No. 21-C. Page 4.1.2.11-1. Appendix K: Serial Presence Detect

(SPD) for DDR3 SDRAM Modules. SPD Revision 1.0.

18) DDR2 FB-DIMM SPD 1.0. Appendix X: Serial Presence Detect (SPD) for Fully

Buffered DIMM (Revision 1.0).

19) JEDEC Standard No. 21-C. Page 4.5.4-1. 168-pin Unbuffered SDRAM DIMM family.

20) JEDEC Standard No. 21-C. Page 4.5.10-1. 184-pin Unbuffered DDR SDRAM DIMM

family.

21) JEDEC Standard No. 21-C. Page 4.5.14-1. 240-pin Unbuffered and Registered

DDR2 SDRAM DIMM family.

22) JEDEC Standard No. 21-C. Page 4.20.19-1. 240-pin

PC3-6400/PC3-8500/PC3-10600/PC3-12800 DDR3 SDRAM Unbuffered DIMM Design

Specification.

Книги

23) В.Л. Григорьев. Микропроцессор i486. Архитектура и программирование.

Москва ТОО "ГРАНАЛ" 1993.

24) В.Г. Артюхов, А.А. Будняк. В.Ю. Лапий. С.М. Молявко, А.И. Петренко.

Проектирование микропроцессорной электронно-вычислительной аппаратуры.

Справочник. Киев "Тэхника" 1988.

25) К. Г. Самофалов, О.В. Викторов. Микропроцессоры. Библиотека инженера. Киев

"Тэхника" 1989.

26) 2B ProGroup: В.А. Вегнер, А.Ю. Крутяков, В.В. Серегин, В.А. Сидоров, А.В.

Спесивцев. Аппаратура персональных компьютеров и ее программирование. IBM

PC/XT/AT и PS/2. Москва "Радио и связь" 1995.