Изучение режимов пзу и озу мультисим. Постоянная память

Отправить свою хорошую работу в базу знаний просто. Используйте форму, расположенную ниже

Студенты, аспиранты, молодые ученые, использующие базу знаний в своей учебе и работе, будут вам очень благодарны.

Размещено на http://www.allbest.ru/

Курсовая работа на тему

Разработка микропроцессорной системы с заданными параметрами ОЗУ и ПЗУ

Введение

2. Расширение адресного пространств

Заключение

Список литературы

Введение

Замечательным свойством микропроцессорных систем является их высокая гибкость, возможность быстрой перенастройки при необходимости даже значительных изменений алгоритмов управления. Перенастройка осуществляется программным путем без существенных производственных затрат. Создание микропроцессоров позволяет уменьшить стоимость и размеры технических средств обработки информации, увеличить их быстродействие, снизить энергопотребление.

Характерные особенности микропроцессорных информационно-управляющих систем, предназначенных для автоматизации технологических процессов:

*наличие ограниченного набора четко сформулированных задач;

*требования оптимизации структуры системы для конкретного применения;

*работа в реальном масштабе времени, т.е. обеспечение минимального времени реакции на изменение внешних условий;

*наличие развитой системы внешних устройств, их большое разнообразие;

*существенное различие функциональных задач;

*высокие требования по надежности с учетом большой продолжительности непрерывной работы;

*сложные условия эксплуатации;

*обеспечение автоматического режима работы или режима с участием оператора как элемента системы.

Целью данной курсовой работы является разработка микропроцессорной системы с заданными параметрами ОЗУ и ПЗУ, а также расчет и проектирование дополнительного ОЗУ и проверка компонентов системы на электрическое взаимодействие.

1. Деление адресного пространства

Существует микропроцессорная система с модулем процессора, обладающим характеристиками:

· тип системной магистрали - с раздельными шинами;

· размер адресного пространства запоминающих устройств (объем ЗУ) - 64 к;

· разрядность шины данных запоминающих устройств - 16;

организация системы ввода/вывода:

· количество портов ввода/вывода - 2048;

· разрядность шины данных портов ввода/вывода - 16;

сигналы шины управления:

· - запись в запоминающее устройство;

· - чтение из запоминающего устройства;

· - запись во внешнее устройство;

· - чтение из внешнего устройства;

Подсоединим к микропроцессорной системе модуль памяти, содержащий: ПЗУ, ОЗУ1 и ОЗУ2.

Количество слов ПЗУ (ПЗУкс) вычислим по формуле:

ПЗУкс=2 ММ =2 01 =2

Количество слов ОЗУ2 (ОЗУ2кс) вычисляем следующим образом:

1. вычислить возможное количество слов Y по формуле:

Y = (ЗУап - ПЗУкс) / 3=(64*1024-2*16)/3=21 (к)

2. полученное количество слов Y округлить до ОЗУ2кс, удовлетворяющей следующим условиям:

а) ОЗУ2кс? Y;

б) ОЗУ2кс кратен 2 n (n = 0, 1, 2, …).

n=4, 2 n =16 ? 21.

Количество слов Y = 16

Количество слов ОЗУ1 (ОЗУ1кс) вычислить по формуле:

1. вычислить возможный объем Y по формуле:

Y = (ЗУап - ПЗУкс - ОЗУ2кс) / 3=(64*1024-2*16-16*16)/3=21 (к)

2. полученное количество слов Y округлить до ОЗУ1кс, удовлетворяющей следующим условиям:

а) ОЗУ1кс? Y;

б) ОЗУ1кс кратен 2 n (n = 0, 1, 2, …)

n=4, 2 n =16 ? 21.

Микросхема ПЗУ содержит: 1 адресный вход по количеству слов, подаваемых на вход, 8 выходов данных для подключения ОЗУ, входы для управляющих сигналов - выбор кристалла и EO - состояние выхода.

Микросхемы ОЗУ1 и ОЗУ2 содержат: по 4 адресных входа, совмещенные входы/выходы данных, входы для управляющих сигналов CS - выбор кристалла, /R-запись/чтение.

Спроектируем элемент микросхемы ПЗУ с помощью инструментария приложения MS Visio 2010 как показано на рисунке 1.

Рисунок 1. Проект микросхемы ПЗУ

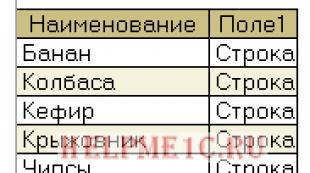

Подберем подходящий аналог, воспользовавшись . Предварительно отобразим в таблице назначение выводов микросхем, как показано в Табл. 1.

Таблица 1. Обозначение выводов микросхем памяти

|

Наименование |

Обозначение |

|

|

Тактовый сигнал |

||

|

Строб адреса столбца |

||

|

Строб адреса строки |

||

|

Выбор микросхемы |

||

|

Разрешение |

||

|

Считывание |

||

|

Запись - Считывание |

||

|

Разрешение записи |

||

|

Разрешение по выходу (считывания) |

||

|

Данные (информация) |

||

|

Входные данные |

||

|

Выходные данные |

||

|

Адрес, данные:вход, выход |

||

|

Данные: вход, выход |

||

|

Регенерация |

||

|

Программирование |

||

|

Стирание |

||

|

Напряжение питания |

||

|

Напряжение программирования |

||

|

Общий вывод микросхемы |

Микросхемы ПЗУ по способу занесения в них информации делятся на три группы: масочные ПЗУ, однократно программируемые по способу шаблона (маски), однократно программируемые по способу прожигания перемычек на кристалле ППЗУ, многократно программируемые пользователем РПЗУ.

При проектировании микросхем, если объем RAM невелик (до 1024 бит), то память набирают из отдельных триггеров. В ином случае пользуются библиотеками готовых модулей памяти. При разработке проекта для ПЛИС готовые модули памяти имеют объем 16, 32, 2048, 4096 бит. В последних сериях ПЛИС объем модуля RAM возрос до 16К или 18К бит. Разрядность модуля RAM может задаваться из ряда: 1,2,4,8 и 16 бит. Запись данных и адреса в модуль RAM всегда выполняется по фронту синхросерии или сигнала записи, т.е. вход модуля можно рассматривать как вход синхронного регистра. Чтение данного чаще всего выполняется в следующем такте после такта приема адреса. Иногда на выходе модуля RAM стоит синхронный регистр, запоминающий прочитанное слово. Запись и чтение из модуля может выполняться по конвейерному принципу: в одном такте записывается адрес нового данного и выдается прочитанное данное по предыдущему адресу. Для формирования RAM большого объема собирают систему из нескольких готовых модулей, дешифратора адреса для селекции модуля и выходного мультиплексора. Различные варианты RAM в лабораторной работе имеют три, две или одну шину. В первом случае шины входного, выходного данного и адреса - раздельны, во втором случае шина входного и выходного данного совмещены и в третьем случае и адрес, и данные передаются по одной шине мультиплексированно.

В соответствии с заданием выберем масочную ПЗУ, структурная схема, которой показана на рисунке 2.

Рисунок 2. Структурная схема масочной ПЗУ

Программирование микросхем ПЗУМ осуществляется однократно. Микросхема обладает свойством энергозависимости. Микросхемы ПЗУМ работают в режимах: считывания и хранения. Для считывания информации необходимо подать код адреса и разрешающие сигналы управления.

Подобранный тип микросхемы и соответствующие характеристики изображены на рисунке 3.

Рисунок 3. Вид микросхемы

Выбираем микросхему KP1610PE1. Характеристики микросхемы показаны в таблице 2.

Таблица 2

|

Тип микросхемы |

Емкость, бит |

P пит, мВт |

Тип выхода |

|||

Спроектируем элемент микросхемы ОЗУ с помощью инструментария приложения MS Visio 2010 как показано на рисунке 4.

микросхема запоминающий электрический

Рисунок 4. Проект микросхемы ОЗУ

2. Расширение адресного пространства

К микропроцессорной системе, спроектированной в прошлом разделе, подсоединяем дополнительный модуль оперативного запоминающего устройства (ОЗУд), содержащее N слов. Для определения количества слов памяти необходимо:

1. определить размер свободного, наибольшего, участка адресного

пространства запоминающих устройств, Y;

Y=(ЗУап - ПЗУкс - ОЗУ2кс- ОЗУ1кс) / 3=(64*1024-2*16-16*16-16*16)/3=21 (к)

2. размер Y округлить до N слов удовлетворяющих следующим условиям:

б) N кратен 2 n (n=0,1,2,…).

ОЗУд содержит: 7 адресных входов, совмещенные входы/выходы данных, входы для управляющих сигналов - выбор кристалла, -запись, -чтение.

3. Электрическое взаимодействие микропроцессорных компонентов

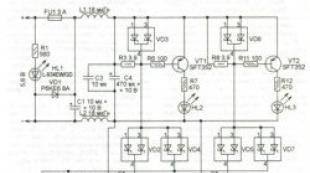

Произведем проверку электрического сопряжения элементов микропроцессорной системы, используя принципиальную электрическую схему микропроцессорной системы, реализованную на базе реальных элементов.

В расчетах используем характеристики приведенные ниже.

1. Модуль процессора:

I0вх, мА? - 2

I1вх, мА? 0,05

Uпит, В = 5 ± 5%.

U1вых, В? 2,7

U0вых, В? 0,5

I0вых, мА? 100

I1вых мА? -5

Cвых, пФ? 10

Устройство ввода, устройство ввода/вывод:

I0вх, мА? -1,6

I1вх, мА? 0,04

Uпит, В = 5 ± 5%.

U1вых, В? 2,7

U0вых, В? 0,5

I0вых, мА? 48

I1вых мА? -2,4

Cвых, пФ? 10

Остальные микросхемы в соответствии с паспортными данными.

Заключение

В настоящее время доля электронных информационных устройств и устройств автоматики непрерывно увеличивается. Это является результатом развития интегральной технологии, внедрение которой позволило наладить массовый выпуск дешевых, высококачественных, не требующих специальной настройки и наладки микроэлектронных функциональных узлов различного назначения, основой которых являются такие элементы электроники как полупроводниковые приборы. Создание разнообразных и замечательных по своим свойствам полупроводниковых приборов обусловили современные успехи электроники.

Чтобы изучить современную электронику, надо, прежде всего, познать принципы устройства и физические основы работы этих приборов, их характеристики, параметры и важнейшие свойства, определяющие возможности их применения. При этом очень важным являются оперативность и точность получения информации, чему должно способствовать использование различных технических средств.

В данной курсовой работе были разработаны принципиальные электрические схемы и подобраны компоненты микросхем в соответствии с заданным вариантом, а также исследованы возможности их замены и расширения.

Список литературы

1. Лучший поисковик электронных компонентов

2. ***RUSSIAN ELECTRONIC***

3. РадиоФанат

4. Телемастер

5. Промэлектроника

6. РЫНОК МИКРОЭЛЕКТРОНИКИ (справочник)

7. ЭЛЕКТРОННЫЕ КОМПОНЕНТЫ СО ВСЕГО МИРА

8. ПРАКТИЧЕСКАЯ ЭЛЕКТРОНИКА

9. РадиоЛоцман -- Схемы

10. Митинский радиорынок

11. Конференция «Микроконтроллеры и их применение»

12. ООО "Микро-Чип"

13. Виртуальный магазин DESSY

14. Русскоязычная страница ATMEL

15. Schemes Site (принцип.схемы)

16. СПРАВОЧНИК ПО РАДИОДЕТАЛЯМ

Размещено на Allbest.ru

Подобные документы

Применение цифровых микросхем для вычисления, управления и обработки информации. Назначение микропроцессора и устройств микропроцессорной системы, их структурная и принципиальная схемы. Системная шина процессора и распределение адресного пространства.

курсовая работа , добавлен 29.02.2012

Расчет статического модуля оперативной памяти и накопителя. Построение принципиальной схемы и временной диаграммы модуля оперативного запоминающего устройства. Проектирование арифметико-логического устройства для деления чисел с фиксированной точкой.

курсовая работа , добавлен 13.06.2015

Иерархия запоминающих устройств ЭВМ. Микросхемы и системы памяти. Оперативные запоминающие устройства. Принцип работы запоминающего устройства. Предельно допустимые режимы эксплуатации. Увеличение объема памяти, разрядности и числа хранимых слов.

курсовая работа , добавлен 14.12.2012

Разработка структуры корпоративной информационной системы. Проектирование адресного пространства. Обоснование выбора аппаратной конфигурации клиентских станций и серверного оборудования. Расчет стоимости оборудования и программного обеспечения системы.

курсовая работа , добавлен 15.02.2016

Рассмотрение структурной схемы микропроцессорной системы обработки данных. Описание архитектуры микроконтроллера ATmega161. Расчет оперативного запоминающего устройства. Строение, назначение адаптера параллельного интерфейса, способы его программирования.

курсовая работа , добавлен 24.09.2010

Назначение и устройство микропроцессорной системы контроля. Описание функциональной схемы микропроцессорной системы контроля. Расчет статической характеристики канала измерения. Разработка алгоритма функционирования микропроцессорной системы контроля.

курсовая работа , добавлен 30.08.2010

Разработка структурной схемы и обобщенного алгоритма работы прибора. Оценка максимальной погрешности линейного датчика давления и нормирующего усилителя. Разработка элементов принципиальной электрической схемы микропроцессорной системы сбора данных.

курсовая работа , добавлен 08.02.2015

Анализ вариантов проектных решений и выбор на его основе оптимального решения. Синтез функциональной схемы микропроцессорной системы на основе анализа исходных данных. Процесс разработки аппаратного и программного обеспечения микропроцессорной системы.

курсовая работа , добавлен 20.05.2014

Структура аппаратуры передачи информации. Разработка передающей и приемной части в соответствии с заданными параметрами. Разработка функциональной схемы устройства преобразования сигналов и устройства защиты от ошибок, алгоритм его функционирования.

курсовая работа , добавлен 12.03.2009

Структура корпоративной информационной системы организации. Разработка адресного пространства и системы DNS. Структура домена КИС. Выбор аппаратной и программной конфигурации рабочих станций и серверного оборудования. Конфигурирование типовых сервисов.

Лабораторна робота № 8

Тема: Исследование работы оперативного запоминающего устройства (ОЗУ )

1. Цель работы.

Изучить работу оперативного запоминающего устройства в режимах записи и считывания информации, исследовать временные параметры этого устройства.

Используемое оборудование и средства: персональный компьютер, среда Multisim 12 .

Краткие теоретические сведения.

Конструктивно любое ОЗУ состоит из двух блоков - матрицы запоминающих элементов и д е шифратора адреса . По технологическим соображениям матрица чаще всего имеет двухкоорд и натную дешифрацию адреса - по строкам и столбцам. На рис.1 показана матрица 16-битного ст а тического ОЗУ.

Матрица состоит из 16 ячеек памяти mem _ i .

Схема элемента матрицы (одной ячейки п а мяти) приведена на рис.2. Каждая ячейка п а мяти адресуется по входам X , Y путём выб о ра дешифраторами адресных линий по стр о кам Ах0…Ах3 и по столбцам Ау0…Ау3. Выбор осуществляется путем подачи по в ы бранным линиям матрицы сигнала лог. «1». При этом в выбранной ячейке памяти сраб а тывает двухвходовой элемент И (U 1 рис.2), подготавливая цепи чтения-записи информ а ции на входных D 10… D 13 или выходных DO0 … DO 3 разрядных шинах.

Разрешающим сигналом для выдачи адреса является CS , который подаётся на вход ра з решения счётчика адреса (Addr _ cnt ) или т а кой же вход дешифраторов, подключённых к выходам счётчика.

Рис. 1. Матрица 16-битного ОЗУ

При записи бита в ячейку памяти (рис. 2) на соответствующей разрядной шине устанавливается 1 или 0, на входе WR /RD устанавливается «1», после стр о бирования счётчика или дешифратора адреса сигналом CS , срабатывают эл е менты 2И U 1, U 2 . Положительный пер е пад сигнала с элемента U 2 поступает на тактовый вход D -триггера U 4 , в резул ь тате чего в нём записывается 1 или 0, в з а висимости от уровня сигнала на его D -входе.

Рис. 2. Схема ячейки памяти mem _ i .

При чтении из ячейки памяти на входе WR / RD устанавливается 0, при этом срабатывают элеме н ты U 1, U 3, U 5 и на вход РАЗРЕШЕНИЕ ВЫХОДА буферного элемента U 6 поступает разреша ю щий сигнал, в результате чего сигнал с Q -выхода D -триггера передаётся на разрядную шину DO 0… DO 3.

Для проверки функционирования ячейки памяти используется генератор слова (рис. 3).

Рис. 3. Лицевая панель генератора слова с установками для схемы

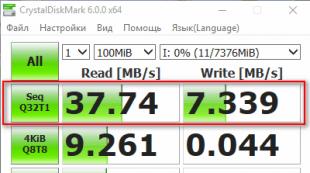

Для исследований режимов работы ОЗУ в лабораторной работе используется микросхема HM-65642/883, которая является ОЗУ статического типа. В отличие от ОЗУ, приведенном на рис.1, имеет объем 8192 x 8-bit ячеек.

Данные для подключения микросхемы HM-65642/883приведены на рис. 4.

Рис. 4. Обозначение выводов микросхемы ОЗУ типа НМ-65642/883.

Управление осуществляется двумя сигналами: G - разрешение выборки, W - разрешение зап и си информ а ции. Адресные входы обозначены А , выходные сигналы обозначаются буквой D .

Порядок выполнения работы.

Експеримент 1 . Исследование ячейки оперативного запоминающего устройства (ОЗУ).

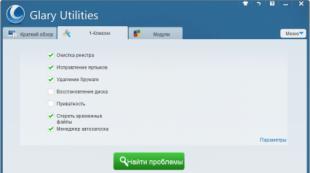

Загрузить программу Multisim 12 из Главного меню.

- Соберите схему, изображенную на рис. 2.

- Изобразите какими должны быть входные и выходные сигналы на элементах И1 И6 при записи, хранении и считывании информации.

- Установите на генераторе слова комбинацию цифр, обеспечивающих запись в ячейку памяти в соответствии с номером варианта двоичной единицы.

- И6.

- Установите на генераторе слова комбинацию цифр, обеспечивающих хранение в упомянутой ячейке памяти двоичной единицы.

- Просмотрите с помощью осциллографа и зарисуйте сигналы на входах и выходах элементов И1 И6.

- Установите на генераторе слова комбинацию цифр, обеспечивающих считывание двоичной единицы с ячейки памяти.

- Просмотрите с помощью осциллографа и зарисуйте сигналы на входах и выходах элементов И1 И6.

Експеримент 2. Исследование матрицы ОЗУ .

- Соберите схему, изображенную на рис. 5.

Рис.5. Схема виртуальной платы с матрицей ОЗУ.

- С помощью клавиш S 1… S 8 задать адреса ячеек области памяти (в соответствии с номером варианта) для считывания содержимого этих ячеек. Результаты записать в виде таблицы:

Адрес Данные

К 0111

К+1 1011

К+2 1101

К+3 1110

- Записать данные с помощью клавиш S 9… S 16 в ячейки ОЗУ в соответствии с номером варианта. Данные индицируются в двоичном коде с помощью светодиодов, а адреса ячеек- с помощью цифровых индикаторов в шестнацатиричном коде.

- Данные, которые записывают в ячейки памяти в соответствии с номером варианта- следующие:

а) бегущий «0»;

б) бегущая «1»;

в) бегущие «00»;

г) бегущие «11»

д) «нарастающий уровень»;

е) «убывающий уровень»;

ж) смена тетрады «11110000»;

з) «чередование» 1010101010.

5. Динамическую индикацию осуществить при переключении клавиш адреса S 1… S 8 на соответствующие выходы счетчика, который переключает адреса ячеек в результате поступления управляющих импульсов с генератора.

6. Исследовать осциллограммы сигналов в режиме считывания данных.

1. Наименование и цель лабораторной работы.

2. Наименование каждого пункта работы, схемы, результаты измерений.

3. Выводы по результатам исследований.

В микропроцессорных системах используется два вида запоминающих устройств (ЗУ): оперативные (ОЗУ) и постоянные (ПЗУ). В ОЗУ основной режим работы - это запись и считывание информации. Информация все время обновляется, хранится не долго и при выключении аппаратуры теряется. В ПЗУ основной режим работы - только считывание информации. Запись происходит при изготовлении микросхемы или при установке ее в аппаратуру.

Различают разновидности ПЗУ: программируемые (ППЗУ) и репрограммируемые (РПЗУ). Программируемые ПЗУ позволяют пользователю самостоятельно при помощи специальных приспособлений однократно записать информацию в микросхему. Такая запись программ производится обычно после их проверки и отладки. Изменить информацию после ее занесения в микросхему невозможно.

Репрограммируемые ПЗУ позволяют многократно стирать и заново заносить информацию. При этом может использоваться электрическое (ЭРПЗУ) или ультрафиолетовое стирание (РПЗУ - УФ).

В зависимости от способа организации памяти различают статические и динамические ЗУ. Статические ЗУ образованы на основе триггерных ячеек. Динамические ЗУ допускают изменение или передвижение данных при хранении, например, запоминание на конденсаторах, требующее периодического восстановления заряда. Динамические ЗУ не позволяют производить считывание в произвольный момент времени, но они обладают очень высокой плотностью записи информации и малым потреблением электроэнергии.

Для изготовления микросхем памяти используется ТТЛ и МОП технология и их разновидности.

На логических схемах ОЗУ обозначается RAM (динамическое ОЗУ-RAM) - Random Acces Memory - память с произвольной выборкой.

ПЗУ обозначается ROM (ППЗУ – PROM, РПЗУ – RPROM) - Read Only Memory - память только со считыванием.

Статические ОЗУ . Промышленностью выпускается большое количество различных микросхем оперативной памяти в различных сериях интегральных схем: К500, К1500, К537, К541, К565.

В качестве примера рассмотрим широко используемую в качестве статического ОЗУ микросхему К537РУЗ - рис.6.6. Она выполнена по КМОП технологии, но по уровню сигналов стыкуется с микросхемами ТТЛ типа. Объем памяти составляет 4К, т.е. 4096 триггерных ячеек. Время выборки не превышает 0,1 мкс, а время восстановления - 70 нс.

Внутри микросхема содержит матрицу 64 х 64 запоминающих элементов, дешифраторы адреса строк и столбцов, усилители записи и считывания, схему управления. Обозначения входов микросхемы:

А 12-разрядный адрес ячейки памяти;

DO output - выход данных;

DI input-вход данных;

CS выбор микросхемы;

WE установка режима «запись - считывание».

Символ на правом обрезе условного обозначения микросхемы обозначает, что выход имеет третье высокоимпендансное состояние Z . Режим работы микросхемы в зависимости от состояния управляющих сигналов иллюстрируется следующей таблицей:

| CS | WE | Di | DO | Режим |

| Di | Z | Запись | ||

| * | DO | Чтение | ||

| * | * | Z | Хранение |

Символ ◊ обозначает произвольное состояние входа.

Объединяя несколько таких микросхем, можно построить многоразрядное ЗУ на 64К слов.

Динамические ОЗУ содержатся в микросхемах серии К565. Емкость их составляет до 64К. Регенерация происходит через каждые 2 мс. Микросхема имеет 4 режима работы: запись, считывание, хранение, регенерация. Регенерация производится путем обращения к каждой ячейке памяти по сигналу RAS. Естественно, в то время, когда происходит регенерация, запись и считывание информации производить нельзя.

Постоянные ЗУ

служат для хранения программ и другой постоянной информации. Микросхемы этого типа сохраняют информацию при выключении напряжения питания. Строятся на базе матрицы запоминающих элементов ТТЛ или МОП структуры. Запись информации в матрицу происходит одноразово при помощи специально изготавливаемого фотошаблона путем металлизации промежутков между элементами. Такой фотошаблон значительно дороже самой микросхемы и изготавливается при заказе большой партии микросхем. Микросхемы ПЗУ входят в состав серий интегральных схем: К500,  К541, К568. К596, К1610. На рнс.6.10 приведена схема ПЗУ К568РЕЗ. В микросхеме может быть записана информация объемом 2 14 байт. Считывание нужного байта производится заданием кода адреса и сигнала CS

выбора микросхемы.

К541, К568. К596, К1610. На рнс.6.10 приведена схема ПЗУ К568РЕЗ. В микросхеме может быть записана информация объемом 2 14 байт. Считывание нужного байта производится заданием кода адреса и сигнала CS

выбора микросхемы.

Программируемые ПЗУ позволяют, задать состояние ячеек памяти не на заводе-изготовителе микросхем, а самим разработчиком микропроцессорной системы. Программирование микросхем ППЗУ происходит путем пережигания плавких вставок в цепях ячеек памяти от внешнего источника с помощью специального устройства - программатора. Такие ПЗУ входят в состав следующих серий микросхем: К500, К556, К537, К541.

Электрические репрограммируемые ПЗУ позволяют осуществить многократное программирование при сохранении памяти при отключении питания. Память сохраняется за счет сохранения заряда в МОП структуре. Длительность хранения информации в нормальных условиях эксплуатации составляет годы.

Количество циклов перепрограммирования может достигать 10 4 . При этом можно стереть или сменить всю информацию или только выборочно. Микросхемы ЭР ПЗУ входят в состав ряда серий интегральных схем: К505, К558,К1601.

РПЗУ с ультрафиолетовым стиранием наиболее распространены. В них снятие заряда с МОП структуры ячейки памяти происходит при ультрафиолетовом облучении кристалла через окошко в корпусе микросхемы. Облучение производят специальной ультрафиолетовой лампой в течение 30 минут.

Примером РПЗУ-УФ может служить микросхема К573РФ. Число циклов перепрограммирования этой микросхемы не менее 25, а время сохранения информации без электропитания не менее 25 × 10 3 часов.

Микросхемы этого типа требуют защиты от случайного воздействия световых потоков во время эксплуатации.

ЛИТЕРАТУРА

1. Забродин Ю.С. Промышленная электроника. - М.: Высшая школа, 1982

2. Исаков Ю.Л. и Др. Основы промышленной электроники. Библиотека инженера. - К.: Техника, 1976.

3. Горбачев В.Н., Чаплыгин Е.Е. Промышленная электроника. - М.: Высшая школа, 1988.

4. Криютафович А. К., Трнфонюк В.В. Основы промышленной электроники. - М.: Высшая школа, 1985.

5. Руденко B.C., Сенько В.И., Трифонюк В.Р. Основы промышленной электроники. - К.: Высшая школа, 1985.

6. Шило В.Л. Популярные цифровые микросхемы. - М.: Радио и связь, 1988.

7. Краснопрошнна А.А., Скаржепа В.А., Кравец П.И. Электроника и микросхемотехника. - К.: Вища школа, 1989.

8. Применение интегральных микросхем. Под ред.А.Уильямса. Перевод с англ. - М.: Мир. 19?".

9. Щербаков В.И., Грездов Г.И. Электронные схемы на операционных усилителях. - К.: Техника, 1983.

10. Гранитов В.И. Физика полупроводников и полупроводниковые приборы. - М.: Советское радио, 1977.

11. Самофалов К.Г., Викторов О.В., Кузняк А.К. Микропроцессоры. Библиотека

инженера.-К.: Техника, 1986.

12.МирскиП Г.Я, Микропроцессоры в измерительных приборах. - М.: Радио и связь. 1984.

13. Вершинин О.Е. Применение микропроцессоров для автоматизации технологических процессов. - Л.: Энергоатомнздат, 1986.

|

3.1.Микросхемы памяти

Преимущество памяти, изображенной на рис. 3.28, состоит в том, что подобная структура применима при разработке памяти большого объема. Мы нарисовали схему 4x3 (для 4 слов по 3 бита каждое). Чтобы расширить ее до размеров 4x8, нужно добавить еще 5 колонок триггеров по 4 триггера в каждой, а также 5 входных и 5 выходных линий. Чтобы перейти от размера 4x3 к размеру 8x3, мы должны добавить еще четыре ряда триггеров по три триггера в каждом, а также адресную линию А2. При такой структуре число слов в памяти должно быть степенью двойки для максимальной эффективности, а число битов в слове может быть любым. Поскольку технология изготовления интегральных схем хорошо подходит для

производства микросхем с внутренней структурой повторяемой плоской поверхности, микросхемы памяти являются идеальным применением для этого. С развитием технологии число битов, которое можно вместить в одной микросхеме, постоянно увеличивается, обычно в два раза каждые 18 месяцев (закон Мура). С появлением больших микросхем маленькие микросхемы не всегда устаревают из-за компромиссов между преимуществами емкости, скорости, мощности, цены и сопряжения. Обычно самые большие современные микросхемы пользуются огромным спросом и, следовательно, стоят гораздо дороже за 1 бит, чем микросхемы небольшого размера.

При любом объеме памяти существует несколько различных способов орга-

низации микросхемы. На рис. 3.30 показаны две возможные структуры микросхемы в 4 Мбит: 512 Кх8 и 4096 Kxl. (Размеры микросхем памяти обычно даются в битах, а не в байтах, поэтому здесь мы будем придерживаться этого соглашения.) На рис. 3.30, а можно видеть 19 адресных линий для обращения к одному из 219 байтов и 8 линий данных для загрузки или хранения выбранного байта.

Сделаем небольшое замечание по поводу терминологии. На одних выводах

высокое напряжение вызывает какое-либо действие, на других - низкое напряжение. Чтобы избежать путаницы, мы будем употреблять термин «установить сигнал»,когда вызывается какое-то действие, вместо того чтобы говорить, что напряжение повышается или понижается. Таким образом, для одних выводов установка сигнала значит установку на 1, а для других - установку на 0. Названия выводов, которые устанавливаются на 0, содержат сверху черту. Сигнал CS устанавливается на 1, а сигнал CS - на 0. Противоположный термин - «сбросить».

А теперь вернемся к нашей микросхеме. Поскольку обычно компьютер содержит много микросхем памяти, нужен сигнал для выбора необходимой микросхемы, такой, чтобы нужная нам микросхема реагировала на вызов, а остальные нет.

Сигнал CS (Chip Select - выбор элемента памяти) используется именно для этой цели. Он устанавливается, чтобы запустить микросхему. Кроме того, нужен способ отличия считывания от записи. Сигнал WE (Write Enable - разрешение записи) используется для указания того, что данные должны записываться, а не считываться. Наконец, сигнал (Ж (Output Enable - разрешение выдачи выходных сигналов) устанавливается для выдачи выходных сигналов. Когда этого сигнала нет, выход отсоединен от остальной части схемы. На рис. 3.30, б используется другая схема адресации. Микросхема представляет собой матрицу 2048x2048 однобитных ячеек, что составляет 4 Мбит. Чтобы обратиться к микросхеме, сначала нужно выбрать строку. Для этого И-битный номер этой строки подается на адресные выводы. Затем устанавливается сигнал RAS (Row Address Strobe - строб адреса строки). После этого на адресные выводы подается номер столбца и устанавливается сигнал CAS (Column Address Strobe - строб адреса столбца). Микросхема реагирует на сигнал, принимая или выдавая 1 бит данных.

Большие микросхемы памяти часто производятся в виде матриц mxn, обращение к которым происходит по строке и столбцу. Такая организация памяти сокращает число необходимых выводов, но, с другой стороны, замедляет обращение к микросхеме, поскольку требуется два цикла адресации: один для строки, а другой для столбца. Чтобы ускорить этот процесс, в некоторых микросхемах можно вызывать адрес ряда, а затем несколько адресов столбцов для доступа к последовательным битам ряда.

Много лет назад самые большие микросхемы памяти обычно были устроены

так, как показано на рис. 3.30, б. Поскольку слова выросли от 8 до 32 битов и выше, использовать подобные микросхемы стало неудобно. Чтобы из микросхем 4096 Kxl построить память с 32-битными словами, требуется 32 микросхемы, работающие параллельно. Эти 32 микросхемы имеют общий объем, по крайней мере, 16 Мбайт. Если использовать микросхемы 512 Кх8, то потребуется всего 4 микросхемы, но при этом объем памяти будет составлять 2 Мбайт. Чтобы избежать наличия 32 микросхем, большинство производителей выпускают семейства микросхем с длиной слов 1,4, 8 и 16 битов.

3.2.ОЗУ и ПЗУ

Все виды памяти, которые мы рассматривали до сих пор, имеют одно общее свойство: в них можно и записывать информацию, и считывать ее. Такая память называется ОЗУ (оперативное запоминающее устройство). Существует два типа ОЗУ: статическое и динамическое. Статическое ОЗУ конструируется с использованием D-триггеров. Информация в ОЗУ сохраняется на протяжении всего времени, пока к нему подается питание: секунды, минуты, часы и даже дни. Статическое ОЗУ работает очень быстро. Обычно время доступа составляет несколько наносекунд. По этой причине статическое ОЗУ часто используется в качестве кэш-памяти второго уровня.

В динамическом ОЗУ, напротив, триггеры не используются. Динамическое

ОЗУ представляет собой массив ячеек, каждая из которых содержит транзистор и крошечный конденсатор. Конденсаторы могут быть заряженными и разряженными, что позволяет хранить нули и единицы. Поскольку электрический заряд имеет тенденцию исчезать, каждый бит в динамическом ОЗУ должен обновляться (перезаряжаться) каждые несколько миллисекунд, чтобы предотвратить утечку данных. Поскольку об обновлении должна заботиться внешняя логика, динамическое ОЗУ требует более сложного сопряжения, чем статическое, хотя этот недостаток компенсируется большим объемом.

Поскольку динамическому ОЗУ нужен только 1 транзистор и 1 конденсатор на бит (статическому ОЗУ требуется в лучшем случае 6 транзисторов на бит), динамическое ОЗУ имеет очень высокую плотность записи (много битов на одну микросхему). По этой причине основная память почти всегда строится на основе динамических ОЗУ. Однако динамические ОЗУ работают очень медленно (время доступа занимает десятки наносекунд). Таким образом, сочетание кэш-памяти на основе статического ОЗУ и основной памяти на основе динамического ОЗУ соединяет в себе преимущества обоих устройств.

Существует несколько типов динамических ОЗУ. Самый древний тип, кото-

рый все еще используется, - FPM (Fast Page Mode - быстрый постраничный режим). Это ОЗУ представляет собой матрицу битов. Аппаратное обеспечение представляет адрес строки, а затем - адреса столбцов (мы описывали этот процесс, когда говорили об устройстве памяти, показанном на рис. 3.30, 6).

FPM постепенно замещается EDO1 (Extended Data Output - память с расши-

ренными возможностями вывода), которая позволяет обращаться к памяти еще до того, как закончилось предыдущее обращение. Такой конвейерный режим не ускоряет доступ к памяти, но зато увеличивает пропускную способность, выдавая больше слов в секунду. И FPM, и EDO являются асинхронными. В отличие от них так называемое синхронное динамическое ОЗУ управляется одним синхронизирующим сигналом. Данное устройство представляет собой гибрид статического и динамического ОЗУ. Синхронное динамическое ОЗУ часто используется при производстве кэш-памяти большого объема. Возможно, данная технология в будущем станет наиболее

предпочтительной и в изготовлении основной памяти.

ОЗУ - не единственный тип микросхем памяти. Во многих случаях данные

должны сохраняться, даже если питание отключено (например, если речь идет об игрушках, различных приборах и машинах). Более того, после установки ни программы, ни данные не должны изменяться. Эти требования привели к появлению ПЗУ (постоянных запоминающих устройств), которые не позволяют изменять и стирать хранящуюся в них информацию (ни умышленно, ни случайно). Данные записываются в ПЗУ в процессе производства. Для этого изготавливается трафарет с определенным набором битов, который накладывается на фоточувствительный материал, а затем открытые (или закрытые) части поверхности вытравливаются.

Единственный способ изменить программу в ПЗУ - поменять целую микросхему. ПЗУ стоят гораздо дешевле ОЗУ, если заказывать их большими партиями, чтобы оплатить расходы на изготовление трафарета. Однако они не допускают изменений после выпуска с производства, а между подачей заказа на ПЗУ и его выполнением может пройти несколько недель. Чтобы компаниям было проще разрабатывать новые устройства, основанные на ПЗУ, были выпущены программируемые ПЗУ. В отличие от обычных ПЗУ, их можно программировать в условиях эксплуатации, что позволяет сократить время выполнения заказа. Многие программируемые ПЗУ содержат массив крошечных плавких перемычек. Можно пережечь определенную перемычку, если выбрать нужную строку и нужный столбец, а затем приложить высокое напряжение к определенному выводу микросхемы.

Следующая разработка этой линии - стираемое программируемое ПЗУ, которое можно не только программировать в условиях эксплуатации, но и стирать с него информацию. Если кварцевое окно в данном ПЗУ подвергать воздействию сильного ультрафиолетового света в течение 15 минут, все биты установятся на 1.

Если нужно сделать много изменений во время одного этапа проектирования, стираемые ПЗУ гораздо экономичнее, чем обычные программируемые ПЗУ, поскольку их можно использовать многократно. Стираемые программируемые ПЗУ обычно устроены так же, как статические ОЗУ. Например, микросхема 27С040 имеет структуру, которая показана на рис. 3.30, а, а такая структура типична для статического ОЗУ.

Следующий этап - электронно-перепрограммируемое ПЗУ, с которого мож-

но стирать информацию, прилагая к нему импульсы, и которое не нужно для этого помещать в специальную камеру, чтобы подвергнуть воздействию ультрафиолетовых лучей. Кроме того, чтобы перепрограммировать данное устройство, его не нужно вставлять в специальный аппарат для программирования, в отличие от стираемого программируемого ПЗУ, Но с другой стороны, самые большие электронно-перепрограммируемые ПЗУ в 64 раза меньше обычных стираемых ПЗУ, и работают они в два раза медленнее. Электронно-перепрограммируемые ПЗУ не могут конкурировать с динамическими и статическими ОЗУ, поскольку они работают в 10 раз медленнее, их емкость в 100 раз меньше, и они стоят гораздо дороже. Они

используются только в тех ситуациях, когда необходимо сохранение информации при выключении питания.

Более современный тип электронно-перепрограммируемого ПЗУ - флэш-память. В отличие от стираемого ПЗУ, которое стирается под воздействием ультрафиолетовых лучей, и от электронно-программируемого ПЗУ, которое стирается по байтам, флэш-память стирается и записывается блоками. Как и любое электронно-перепрограммируемое ПЗУ, флэш-память можно стирать, не вынимая ее из микросхемы. Многие изготовители производят небольшие печатные платы, содержащие десятки мегабайтов флэш-памяти. Они используются для хранения изображений в цифровых камерах и для других целей. Возможно, когда-нибудь флэш-память вытеснит диски, что будет грандиозным шагом вперед, учитывая время доступа в 100 не. Основной технической проблемой в данный момент является то, что флэш-память изнашивается после 10 000 стираний, а диски могут служить годами независимо от того, сколько раз они перезаписывались. Краткое описание

различных типов памяти дано в табл. 3.2.

Лекция 8. Микросхемы управления и сопряжения.

1. Микросхемы процессора.

2. Шины и принципы их работы.

3. Средства сопряжения.

МИНИСТЕРСТВО образования и науки Российской Федерации

ФЕДЕРАЛЬНОЕ Государственное БЮДЖЕТНОЕ образовательное учреждение

высшего профессионального образования

тюменский государственный нефтегазовый университет

институт кибернетики, информатики и связи

КУРСОВАЯ РАБОТА

Построение внутренней памяти процессорной системы

по дисциплине: «Вычислительная техника»

Техническое задание

Вариант – 6

Построить внутреннюю память процессорной системы, состоящую из ПЗУ и статического ОЗУ.

Разрядность ША – 20 , ШД – 8 .

Адреса, покрываемые ПЗУ - 00000-03FFF

Адреса, покрываемые ОЗУ – 80000-9FFFF

Емкость микросхемы ПЗУ - 16K*8

Емкость микросхемы ОЗУ - 64K*4

Введение……………………………………………………………………4

1 Теоритическая часть

1.1 Общая структура МПС…………………………………………………5

1.2 Подсистема памяти МПС………………………………………………7

1.3 Устройства памяти……………………………………………………...9

1.4 Статические ОЗУ. Принципы построения…………………………...11

1.5 Принцип записи/чтения информации………………………………...13

1.6 Построение пространства памяти заданного объема………………..14

2 Практическая часть

2.1 Определение емкости ПЗУ и ОЗУ...…………………………………16

2.2 Структура ПЗУ и ОЗУ……………………………………………........19

2.3 Общая структура памяти……………………………………………...20

Заключение…………………………….……………………………………21

Список литературы…………………………………………………………22

Введение

Информация, циркулирующая в вычислительной системе, хранится в памяти. Основными критериями оценки запоминающего устройства являются показатели емкости, быстродействия и потребляемой мощности.

Компьютерная память обеспечивает поддержку одной из наиважнейшей функций современного компьютера – способность длительного хранения информации.

В зависимости от места нахождения в вычислительной системе память подразделяют на внутреннюю (оперативную, сверхоперативную и постоянную) и внешнюю (различные накопители).

В теоретической части данной работы рассмотрена компьютерная память, ее виды и классификации, в практической части – осуществлено построение внутренней памяти процессорной системы.

В конце работы сделано заключение и приведен список использованной литературы.

1.1 Общая структура МПС

Микропроцессор (МП) – центральная часть любой микропроцессорной системы (МПС) – включает в себя арифметико-логическое устройство (АЛУ) и центральное управляющее устройство (ЦУУ), реализующее командный цикл. МП может функционировать только в составе МПС, включающей в себя, кроме МП, память, устройства ввода/вывода, вспомогательные схемы (тактовый генератор, контроллеры прерываний и прямого доступа к памяти (ПДП), шинные формирователи, регистры-защелки и др.

В любой МПС можно выделить следующие основные части (подсистемы):

внешние устройства (внешние ЗУ + устройства ввода/вывода);

подсистему прерываний;

подсистему прямого доступа в память.

процессорный модуль;

Рисунок 1 – Структура МПС с интерфейсом "Общая шина"

Связь между процессором и другими устройствами МПС может осуществляться по принципам радиальных связей, общей шины или комбинированным способом. В однопроцессорных МПС, особенно 8- и 16-разрядных, наибольшее распространение получил принцип связи "Общая шина", при котором все устройства подключаются к интерфейсу одинаковым образом (Рисунок 1).

Все сигналы интерфейса делятся на три основные группы – данных, адреса и управления. Многочисленные разновидности интерфейсов "Общая шина" обеспечивают передачу по раздельным или мультиплексированным линиям (шинам). Например, интерфейс Microbus, с которым работают большинство 8-разрядных МПС на базе i8080, передает адрес и данные по раздельным шинам, но некоторые управляющие сигналы передаются по шине данных. Интерфейс Q-bus, используемый в микро-ЭВМ фирмы DEC (отечественный аналог – микропроцессоры серии К1801) имеет мультиплексированную шину адреса/данных, по которой эта информация передается с разделением во времени. Естественно, что при наличии мультиплексированной шины в состав линий управления необходимо включать специальный сигнал, идентифицирующий тип информации на шине.

Обмен информацией по интерфейсу производится между двумя устройствами, одно из которых является активным, а другое – пассивным. Активное устройство формирует адреса пассивных устройств и управляющие сигналы. Активным устройством выступает, как правило, процессор, а пассивным – всегда память и некоторые ВУ. Однако иногда быстродействующие ВУ могут выступать в качестве задатчика (активного устройства) на интерфейсе, управляя обменом с памятью.

Концепция "Общей шины" предполагает, что обращения ко всем устройствам МПС производится в едином адресном пространстве, однако, в целях расширения числа адресуемых объектов, в некоторых системах искусственно разделяют адресные пространства памяти и ВУ, а иногда даже и памяти программ и памяти данных.

12 Подсистема памяти МПС

Распределение адресного пространства.

Объем адресного пространства МПС с интерфейсом "Общая шина" определяется главным образом разрядностью шины адреса и, кроме того, номенклатурой управляющих сигналов интерфейса. Управляющие сигналы могут определять тип объекта, к которому производится обращение (ОЗУ, ВУ, стек, специализированные ПЗУ и др.). В случае если МП не выдает сигналов, идентифицирующих пассивное устройство (или они не используются в МПС), – для селекции используются только адресные линии. Число адресуемых объектов составляет в этом случае 2 k , где k - разрядность шины адреса. Будем называть такое адресное пространство "единым". Иногда говорят, что ВУ в едином адресном пространстве "отображены на память", т.е. адреса ВУ занимают адреса ячеек памяти. Пример организации селекции устройств в едином адресном пространстве МПС на базе i8080 и распределение адресного пространства показаны на рисунке 2 и рисунке 3 соответственно.

Рисунок 2 – Структура единого адресного пространства

Рисунок 3 – Пример распределения единого адресного пространства

При небольших объемах памяти в МПС целесообразно использовать некоторые адресные линии непосредственно в качестве селектирующих (Рисунок 4), что позволяет уменьшить объем оборудования МПС за счет исключения селектора адреса. При этом, однако, адресное пространство используется крайне неэффективно.

При использовании информации о типе устройства, к которому идет обращение, можно одни и те же адреса назначать для разных устройств, осуществляя селекцию с помощью управляющих сигналов.

Так, большинство МП выдают в той или иной форме информацию о типе обращения. В результате в большинстве интерфейсов присутствуют отдельные управляющие линии для обращения к памяти и вводу/ выводу, реже - стеку или специализированному ПЗУ. В результате суммарный объем адресного пространства МПС может превышать величину 2 k .

Рисунок 4 – Использование адресных линий для прямой селекции устройств

1.3 Устройства памяти

Устройства памяти микропроцессорной системы (МПС) могут быть внешними (винчестер, дисковод, CD-ROM и т.д.) и внутренними (ОЗУ, ПЗУ).

В данной курсовой работе рассматривается внутренняя память МПС, которая может быть:

постоянной (ROM) или ПЗУ,

оперативной (RAM) или ОЗУ.

В свою очередь ПЗУ по способу записи/перезаписи информации различаются следующим образом.

ПЗУ – постоянные запоминающие устройства, в основу которых положены диодные матрицы. Матрицы прожигаются на заводе-изготовителе, пользователь ничего изменить не может (рисунок 5). При подаче U > U доп диод сгорает, остается перемычка; при сгоревшем диоде U узла = 0; при функционирующем диоде U узла = 1

ППЗУ – перепрограммируемые ПЗУ (матрицы поставляются пользователю с уровнем 1 во всех узлах, пользователь может только один раз прожечь матрицу по своей программе).

РПЗУ – репрограммируемые (т.е. многократно программируемые) ПЗУ.

Рисунок 5 – Элемент диодной матрицы.

По способу стирания информации РПЗУ могут быть: ультрафиолетовыми и электрическими.

Оперативные запоминающие устройства ОЗУ могут быть: динамическими (DRAM) и статическими (SRAM).

В динамических ОЗУ, построенных на МОП-транзисторных ячейках с дополнительной емкостью, информация после считывания пропадает, поэтому требуется ее регенерация (восстановление), а значит, такие ОЗУ при своей очевидной дешевизне имеют низкое быстродействие.

Статические ОЗУ, построенные на триггерных ячейках, хранят информацию после считывания и регенерации не требуют, имеют высокое быстродействие, хотя и существенно дороже динамических ОЗУ.

Современные схемы ОЗУ сочетают в себе обе технологии (SDRAM).

1.4 Статические ОЗУ. Принципы построения

Рисунок 6 – Микросхема статической памяти

Шина адреса (рисунок 6) подключается к микросхеме памяти по N адресным входам: A 0 – A N –1 .

Шина данных подключается по входам/выходам D, количество которых зависит от того, сколько матриц размещено в кристалле.

CS – вход выборки кристалла, управляет подключением буфера данных к шине.

– вход запись/чтения, определяет подключение входного или выходного буфера данных к шине данных.

Рассмотрим принцип выбора ячейки памяти по адресу.

Входы адресной шины подключаются к дешифраторам (DC) строки и столбца матрицы. Предположим, что к микросхеме подключается четыре адресных линии (А 0 – А 3), причем линии А 0 , А 1 подаются на DC строки, а линии А 2 , А 3 – на DC столбца.

Рисунок 7– Выбор ячейки по адресу: а – триггера; б – элемента матрицы

Предположим, что на адресных входах указан адрес 9, т.е. 1001.

Таким образом, DC строки по А 0 =1, А 1 =0 установит 1 на выходе 1, а DC столбца по А 2 =0, А 3 =1 установит 1 на выходе 2.

Во всех узлах матрицы расположены триггеры. Вход синхронизации триггера и его выход на общую для данной матрицы линию данных подключаются, как показано на рисунке 7, а.

Очевидно, что функционировать будет только тот триггер, у которого на входы элемента И от DC строки и DC столбца попадут 1.

В нашем случае будет выбран элемент матрицы, обведенный в кружок (рисунок 7, б).

1.5 Принцип записи/чтения информации

Инициализируем элемент матрицы, подав адрес на адресные входы. Теперь покажем, как будет происходить процесс записи/чтения данных. Заметим, что каждая матрица имеет один общий провод данных, т.е. каждый разряд данных записан в своей матрице. Адресация таких матриц производится параллельно.

Рассмотрим обращение к одному разряду данных. Только при подаче на вход CS уровня 0 (рис. 8) на выходе управляющих схем буферов чтения и записи может появиться 1. Причем на выходе управления буфером записи 1 появится при 0 на входе , а на выходе управления буфером чтения – при 1 на .

Рисунок 8 – Функции входов CS и

1.6 Построение пространства памяти заданного объема

Из микросхем SRAM небольшой емкости можно составить память любого заданного объема. Предположим, что в нашем распоряжении есть микросхемы SRAM емкостью 256×4. Необходимо составить память устройства емкостью 1 Кбайт или 1К×8. Схема 256×4 имеет 4 матрицы по 256 ячеек (256 = 2 8), т.е. схема имеет 8 адресных входов.

Рисунок 9 – Микросхема памяти 256×4

Для того чтобы обеспечить чтение/запись байта информации, надо добавить еще 4 матрицы внешним соединением (т.е. объединить 2 микросхемы).

Получим эквивалентную схему, позволяющую хранить 256 байт информации.

Для построения памяти на 1 Кбайт необходимо 4 таких схемы:

1К = 2 10 ; 2 10 / 2 8 = 2 2 = 4.

Рисунок 10 – Получение эквивалентной схемы 256×8

Доступ к такой памяти осуществляется по 10 адресным линиям (1К = 2 10): непосредственно к схеме подключаются 8 адресных линий, а 2 – к дешифратору, с помощью которого выбирается одно из 4 направлений.

Общая схема памяти (рисунок 11) составлена из эквивалентных схем (рисунок 10), исходная микросхема представлена на рисунке 9.

Рисунок 11 – Схема оперативной статической памяти объемом 1Кбайт

2.1 Практическая часть

Построить внутреннюю память процессорной системы, состоящую из ПЗУ и статического ОЗУ. Процессорная система работает в реальном режиме.

Разрядность ША - 20, ШД - 8.

|

от 00000 до 03FFF |

от 80000 до 9FFFF |

Определение емкости ПЗУ и ОЗУ

По полученному диапазону адресов определим емкость ПЗУ и ОЗУ.

Определим количество изменяющихся разрядов и запишем адрес в двоичном коде.

ПЗУ от 00000 до 03FFF

Начальный адрес: 00000000000000000000 2 .

Конечный адрес: 00000011111111111111 2 .

Изменились 14 разрядов, значит, емкость ПЗУ - 2 14 .

Для 8-разрядной шины данных емкость ПЗУ 2 14 *8:

2 14 = 2 10 *2 4 ,

2 10 = 1К - килобайт, таким образом, емкость ПЗУ равна 16К*8.

ОЗУ от 80000 до 9FFFF

Начальный адрес: 10000000000000000000 2 .

Конечный адрес: 10011111111111111111 2 .

Изменилось 17 разрядов.

Для 8-разрядной шины данных емкость ОЗУ равна:

2 17 = 2 10 *2 7

2 10 = 1К - килобайт, таким образом, емкость ОЗУ равна 128К*8.

Для изображения схемы необходимо определить емкости микросхем ОЗУ и ПЗУ. ПЗУ имеет емкость 16К*8 (рис. 1), а ОЗУ - 64К*4 (рис. 2).Таким образом, схема ПЗУ имеет 14 адресных входов 16К = 2 14 , восемь вход/ выход данных и вход CS (выборки кристалла). Схема ОЗУ имеет 17 адресных входов 128К= 2 17 , четыре вход/выход данных, входы CS и

Рисунок 1 - Микросхема ПЗУ 16К*8

Рисунок 2 - Микросхема ОЗУ 64К*4

Структура ПЗУ

Емкость ПЗУ - 16К*8. Емкость микросхемы 16К*8, значит, для получения нужной емкости ПЗУ построить одну микросхему (рис. 3).

Рисунок3 - Структура ПЗУ 16К*8

Структура ОЗУ

Емкость ОЗУ 128К*8, емкость микросхемы 64К*4, значит, для построения такого ОЗУ необходимо построить 2 микросхемы.

Рисунок 4 - Структура ОЗУ 128К*8

Общая структура памяти

По заданию начальные адреса ПЗУ и ОЗУ следующие:

ПЗУ (00000 – 00000000000000000000 2),

ОЗУ (80000 –10000000000000000000 2).

По состоянию разрядов: А19, А18 - 00 работает ПЗУ, а по состоянию А19, А18 - 01 работает ОЗУ. С помощью простейшей логики можно

построить дешифратор направлений ПЗУ/ОЗУ (рис. 5).

Рисунок 5 - Дешифратор направлений ПЗУ-ОЗУ

Рисунок 6 - Общая структура проектируемой памяти

Заключение

В данной курсовой работе была осуществлена задача разработки блока внутренней памяти процессорной системы, состоящую из ПЗУ и статического ОЗУ. Были описаны в аналитическом, структурном и расчетно-графическом виде все необходимые узлы и элементы.

При расчете данной курсовой работы использовались математические и графические пакеты, такие как:

Список литературы

1 Угрюмов Е.П. Цифровая схемотехника. СПб: БХВ-СПб, 2000.

2 Большие интегральные микросхемы запоминающих устройств: справочник. М.: Радио и связь, 1990.